ENERGY-EFFICIENT FLOW-CONTROL FOR ON-CHIP NETWORKS

A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

> Georgios Michelogiannakis June 2012

## Abstract

With the emergence of on-chip networks, the power consumed by router buffers has become a primary concern. Bufferless flow control has been proposed to address this issue by removing router buffers and handling contention by dropping or deflecting flits. In this thesis, we compare virtual-channel (buffered) and deflection (packetswitched bufferless) flow control. Our study shows that unless process constraints lead to excessively costly buffers, the performance, cost and increased complexity of deflection flow control outweigh its potential gains. To provide buffering in the network but without the cost and timing overhead of router buffers, we propose elastic buffer (EB) flow control which adds simple control logic in the channels to use pipeline flip-flops (FFs) as EBs with two storage locations. This way, channels act as distributed FIFOs and input buffers as well as the complexity for virtual channels (VCs) are no longer required. Therefore, EB networks have a shorter cycle time and offer more throughput per unit power than VC networks. We also propose a hybrid EB-VC router which is used to provide traffic separation for a number of traffic classes large enough for duplicate physical channels to be inefficient. These hybrid routers offer more throughput per unit power than both EB and VC routers. Finally, this thesis proposes packet chaining, which addresses the tradeoff between allocation quality and cycle time traditionally present in routers with VCs. Packet chaining is a simple and effective method to increase allocator matching efficiency to be comparable or superior to more complex and slower allocators without extending cycle time, particularly suited to networks with short packets.

## Acknowledgements

First and foremost, I would like to thank my academic advisor Prof. William J. Dally. Bill has shown tremendous commitment to teaching and mentoring. I have always found it remarkable how he is able to fit in individual and group meetings with students in his schedule even though his list of responsibilities keeps growing, especially when he was chairing the Computer Science department. Bill has supported me over the years in more ways than I can possibly remember. He has always given me space to develop my own creativity, has always believed that I could handle everything that came up, and has provided me with opportunities. In addition, Bill is a remarkable individual because he has many impressive hobbies and he excels in all of them. Overall, Bill is an amazing role model.

I would also like to thanks Prof. Christos Kozyrakis for his support and mentoring over the years, as well as serving as a member of my reading committee. Also, I would like to thank Prof. Nick Mckeown for eagerly acceptive to be the third member of my reading committee.

Of course, these five years of my life were made enjoyable with the company of my close friends, with whom I have had some great moments away from stress of graduate school. I would especially like to thank Christine Moore, Daniel Sanchez, Christina Delimitrou, Elliot English, Panagiotis Tsiligkiris, George Karakonstantakis and other members of the Greek community in Stanford. I can only hope to keep in touch in the future.

Furthermore, I thank members of the CVA group, especially those who were admitted in the same year as me and therefore spent most of the time with me: Curt Harting, Nan Jiang and Daniel Becker. Daniel deserves a special mention for being my officemate which means that we shared many humorous moments together. I would also like to thank David Black-Schaffer for introducing me to the *Selection Natural* soccer team in which I had the opportunity to play soccer with some great friends. Finally, I would like to thank James Chen for introducing me to tennis and table tennis.

Last but not least, I would like to thank my family and friends back in Greece for their support and encouragement during my time at Stanford as well as for my future endeavours. My parents have been especially understanding when it came to the difficulties and duration of a PhD.

The work in this thesis was supported in part by the National Science Foundation under Grant CCF-0702341, in part by the National Security Agency under Contract H98230-08-C-0272-P007 and in part by the Robert Bosch Stanford Graduate Fellowship.

# Contents

| 1        | $\mathbf{Intr}$ | oduction                                     | 1  |

|----------|-----------------|----------------------------------------------|----|

|          | 1.1             | Overview of On-Chip Networks                 | 3  |

|          |                 | 1.1.1 Basic Architecture of On-Chip Networks | 3  |

|          |                 | 1.1.2 Topology                               | 6  |

|          | 1.2             | On-Chip Network Consumption and Motivation   | 8  |

|          | 1.3             | Thesis Overview                              | 12 |

|          | 1.4             | Thesis Contributions                         | 16 |

|          | 1.5             | Thesis Structure                             | 17 |

| <b>2</b> | Buf             | ferless Flow Control                         | 18 |

|          | 2.1             | Methodology                                  | 19 |

|          | 2.2             | Routing in Bufferless Networks               | 21 |

|          | 2.3             | Router Microarchitecture                     | 24 |

|          |                 | 2.3.1 Allocator Complexity                   | 24 |

|          |                 | 2.3.2 Buffer Cost                            | 26 |

|          | 2.4             | Evaluation                                   | 27 |

|          |                 | 2.4.1 Latency and Throughput                 | 30 |

|          |                 | 2.4.2 Power and Area Breakdown               | 36 |

|          |                 | 2.4.3 Low-swing Channels                     | 37 |

|          |                 | 2.4.4 Deadlock and Endpoint Buffers          | 37 |

|          |                 | 2.4.5 Flit Injection                         | 39 |

|          |                 | 2.4.6 Credits                                | 39 |

|          |                 | 2.4.7 Process Technology                     | 40 |

|   | 2.5  | Discus  | ssion                                                                    | 40        |

|---|------|---------|--------------------------------------------------------------------------|-----------|

|   | 2.6  | Summ    | nary                                                                     | 42        |

| 3 | Elas | stic Bu | iffer Flow Control                                                       | <b>44</b> |

|   | 3.1  | Elasti  | c Buffer Channels                                                        | 46        |

|   | 3.2  | Elasti  | c Buffer Routers                                                         | 48        |

|   |      | 3.2.1   | Two-Stage Router                                                         | 48        |

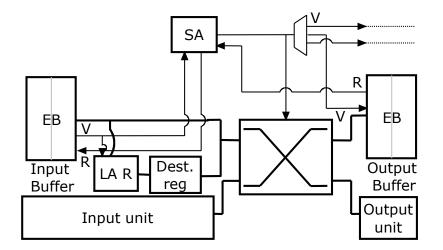

|   |      | 3.2.2   | Single-Cycle Router                                                      | 52        |

|   |      | 3.2.3   | Buffered Crossbar EB Router                                              | 53        |

|   | 3.3  | Deadl   | ock Avoidance and Traffic Classes                                        | 54        |

|   |      | 3.3.1   | The Interleaving Deadlock                                                | 54        |

|   |      | 3.3.2   | Duplicating Physical Channels                                            | 55        |

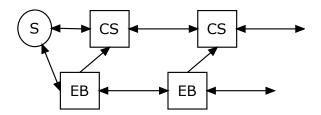

|   |      | 3.3.3   | Using Circuit-Switching in EB Networks for Traffic Separation            | 57        |

|   | 3.4  | Hybri   | d EB Routers                                                             | 58        |

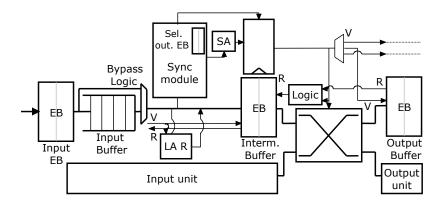

|   |      | 3.4.1   | Hybrid EB-VC Routers                                                     | 59        |

|   |      | 3.4.2   | Hybrid EB-Wormhole Routers                                               | 62        |

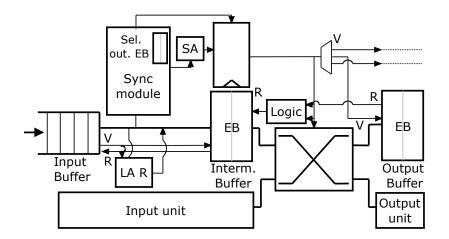

|   | 3.5  | Conge   | estion Sensing                                                           | 66        |

|   |      | 3.5.1   | Congestion Sensing Mechanism                                             | 66        |

|   |      | 3.5.2   | Adaptive Routing                                                         | 69        |

|   | 3.6  | Metho   | odology                                                                  | 72        |

|   | 3.7  | Evalua  | ation                                                                    | 76        |

|   |      | 3.7.1   | EB and VC Network Comparison                                             | 76        |

|   |      | 3.7.2   | Buffer Cost Impact                                                       | 82        |

|   |      | 3.7.3   | Elastic Buffer Router Design Comparison                                  | 85        |

|   |      | 3.7.4   | Hybrid EB-VC Networks                                                    | 91        |

|   |      | 3.7.5   | Wormhole and Hybrid EB-Wormhole Routers                                  | 94        |

|   | 3.8  | Summ    | nary                                                                     | 106       |

| 4 | Pac  | ket Cł  | naining                                                                  | 108       |

|   | 4.1  | Detail  | ed Description                                                           | 110       |

|   |      | 4.1.1   | Conventional Allocation with Short Packets $\ldots \ldots \ldots \ldots$ | 110       |

|   |      | 4.1.2   | Packet Chaining Description                                              | 112       |

|    |       | 4.1.3  | Chaining Variations                                                                                                                         | 116 |

|----|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    |       | 4.1.4  | Packet Chaining Pipeline                                                                                                                    | 117 |

|    |       | 4.1.5  | Starvation Control                                                                                                                          | 120 |

|    | 4.2   | Metho  | dology                                                                                                                                      | 121 |

|    | 4.3   | Evalua | $tion \ldots \ldots$ | 123 |

|    |       | 4.3.1  | Throughput Under Heavy Load                                                                                                                 | 123 |

|    |       | 4.3.2  | Comparing with Other Allocators                                                                                                             | 124 |

|    |       | 4.3.3  | Saturation Throughput and Latency                                                                                                           | 127 |

|    |       | 4.3.4  | Packet Length                                                                                                                               | 130 |

|    |       | 4.3.5  | Optimal Packet Chaining Scheme                                                                                                              | 133 |

|    |       | 4.3.6  | Packet Chaining Probability                                                                                                                 | 134 |

|    |       | 4.3.7  | Starvation and Priorities                                                                                                                   | 136 |

|    |       | 4.3.8  | Application Performance                                                                                                                     | 138 |

|    |       | 4.3.9  | Packet Chaining Cost                                                                                                                        | 140 |

|    | 4.4   | Summ   | ary                                                                                                                                         | 143 |

| 5  | Rela  | ated W | Vork                                                                                                                                        | 145 |

| 6  | Con   | clusio | ns                                                                                                                                          | 152 |

|    | 6.1   | Future | Work                                                                                                                                        | 155 |

| Bi | bliog | raphy  |                                                                                                                                             | 158 |

# List of Tables

| 1.1 | Comparison of two popular topologies for a CMP system                      | 7   |

|-----|----------------------------------------------------------------------------|-----|

| 2.1 | Allocator synthesis comparison.                                            | 26  |

| 3.1 | Two-stage EB network percentage gains compared to VC                       | 78  |

| 3.2 | Two-stage EB and VC router implementation comparison                       | 81  |

| 3.3 | Comparison of the single-stage and two-stage EB routers depending on       |     |

|     | design priority.                                                           | 91  |

| 3.4 | Gates, cells and nets after PnR for EB and wormhole routers. $\ . \ . \ .$ | 98  |

| 4.1 | Packet chaining versus iSLIP-1 using application benchmarks                | 138 |

# List of Figures

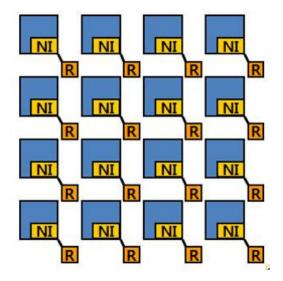

| 1.1  | Abstract illustration of a multi-core architecture.                                                               | 3  |

|------|-------------------------------------------------------------------------------------------------------------------|----|

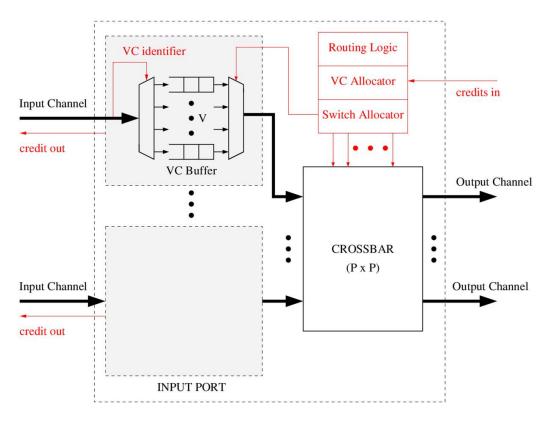

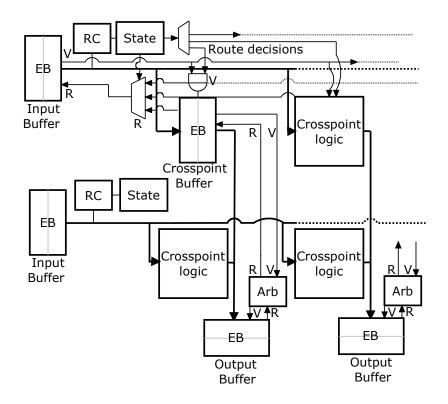

| 1.2  | Architecture of a typical VC router                                                                               | 4  |

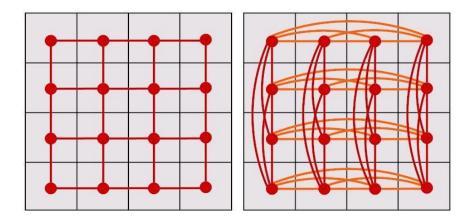

| 1.3  | Two representative on-chip network topologies in a 2D layout. $\ldots$                                            | 6  |

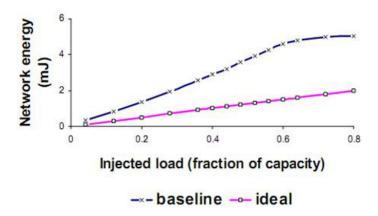

| 1.4  | The power consumption gap between realistic on-chip networks and                                                  |    |

|      | the ideal interconnect. $\ldots$ | 9  |

| 1.5  | Overview of the Intel 80-core Teraflop processor                                                                  | 10 |

| 1.6  | Power breakdown of a single tile in the Intel 80-core Teraflop processor.                                         | 11 |

| 1.7  | Network power breakdown in the Intel 80-core Teraflop processor                                                   | 12 |

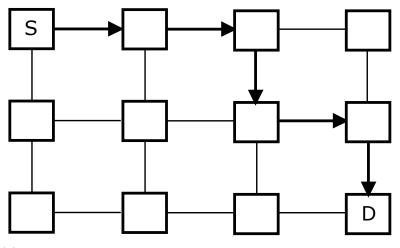

| 2.1  | MDR and PMDR routing algorithms for deflection bufferless networks.                                               | 22 |

| 2.2  | Comparison of DOR, MDR and PMDR routing algorithms                                                                | 23 |

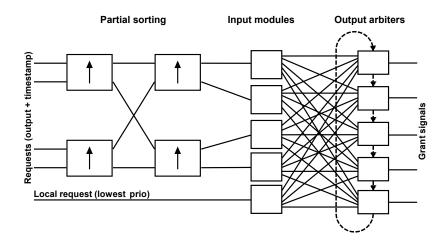

| 2.3  | BLESS allocator implementation.                                                                                   | 25 |

| 2.4  | Empty buffer bypassing.                                                                                           | 25 |

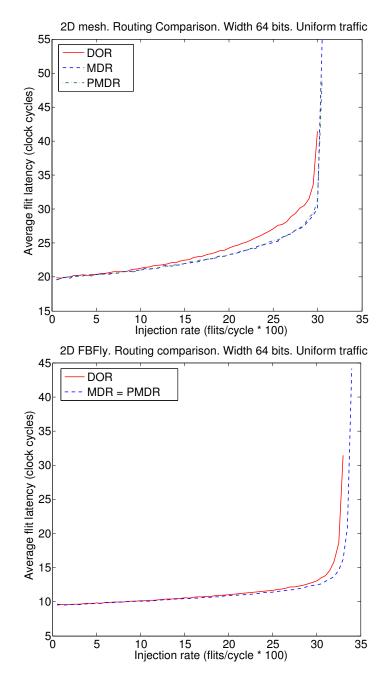

| 2.5  | Mesh latency and power comparison.                                                                                | 28 |

| 2.6  | FBFly latency and power comparison.                                                                               | 29 |

| 2.7  | Blocking and deflection latency distribution.                                                                     | 31 |

| 2.8  | Mesh throughput versus power and area Pareto-optimal curves                                                       | 32 |

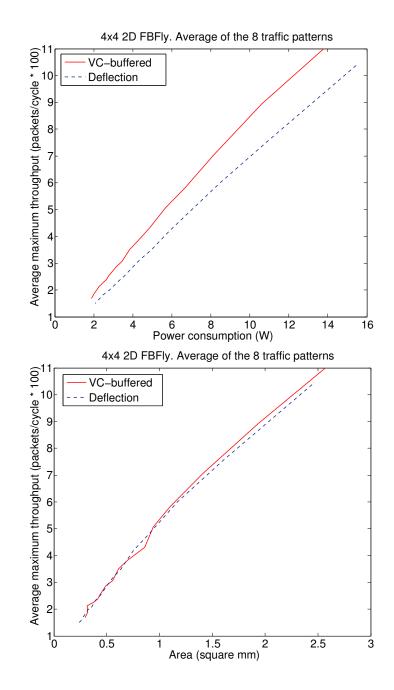

| 2.9  | FBFly throughput versus power and area Pareto-optimal curves                                                      | 33 |

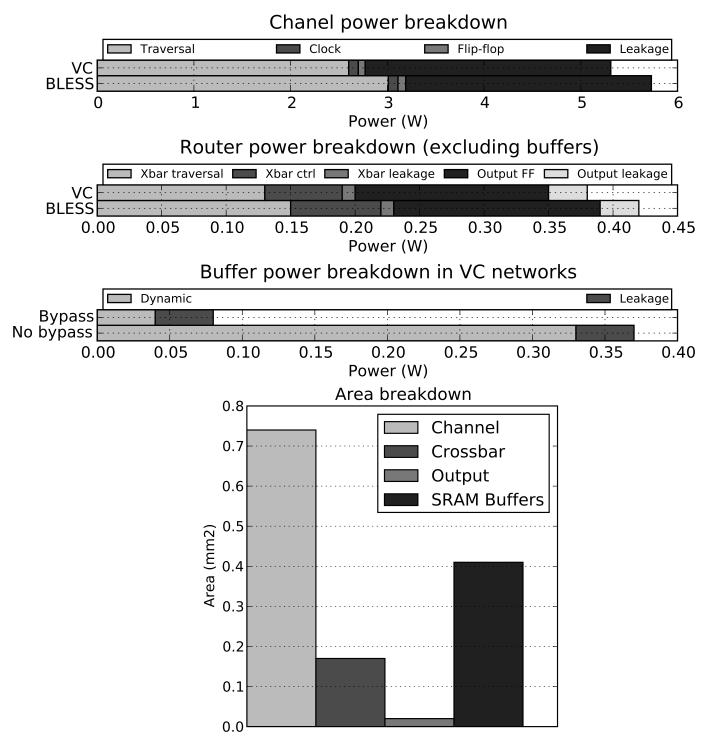

| 2.10 | Power and area breakdowns for the VC network in a 2D mesh                                                         | 34 |

| 2.11 | Power assuming no empty buffer bypassing                                                                          | 35 |

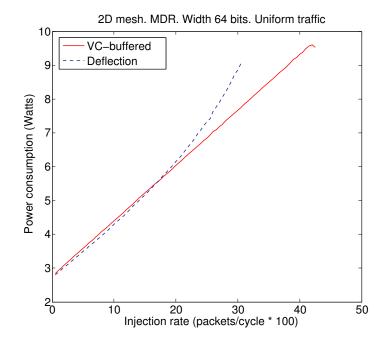

| 2.12 | Power consumption with varying injection rate and throughput-power                                                |    |

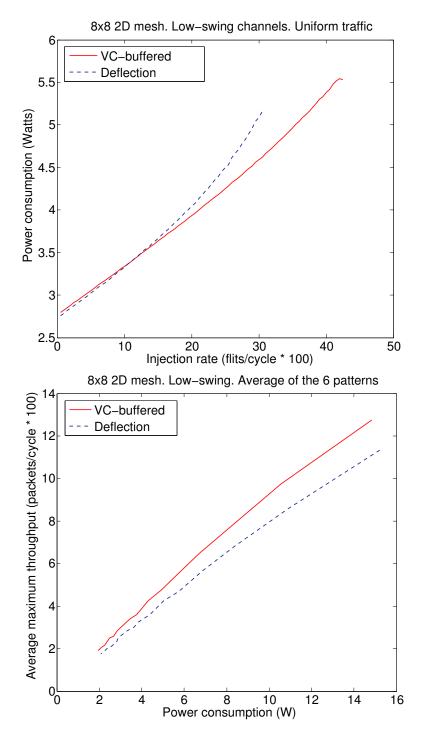

|      | Pareto-optimal curves with low-swing channels.                                                                    | 38 |

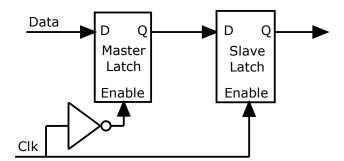

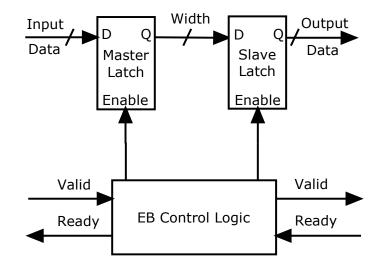

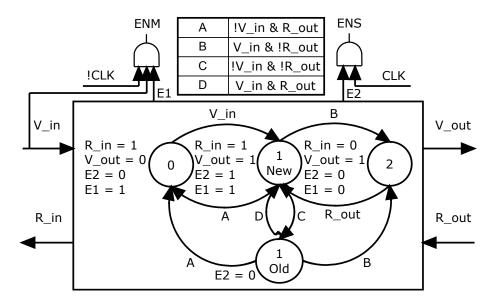

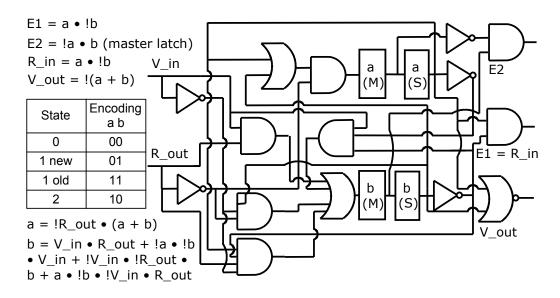

| 3.1  | A DFF implemented with a master and a slave D latch                                                               | 45 |

| 3.2  | Expanded view of the EB control logic as a synchronous FSM for two-          |

|------|------------------------------------------------------------------------------|

|      | slot EBs                                                                     |

| 3.3  | Expanded view of the EB control logic as a synchronous FSM for two-          |

|      | slot EBs                                                                     |

| 3.4  | Logic diagram of the EB control FSM with 2 FFs and 10 gates. $\dots$ 47      |

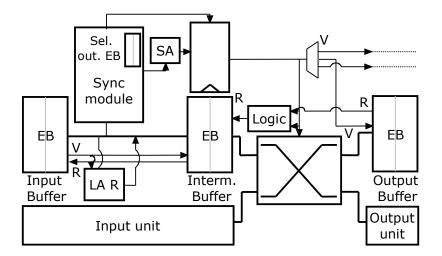

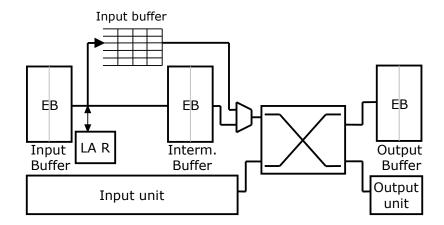

| 3.5  | A two-stage EB router                                                        |

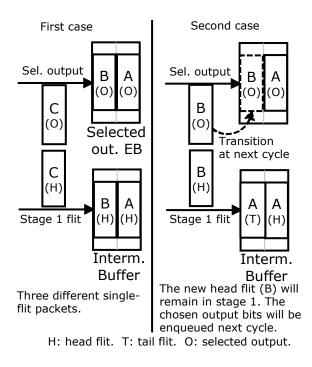

| 3.6  | Two-stage EB router synchronization module operation                         |

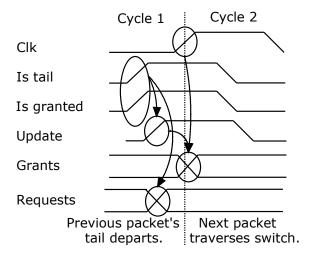

| 3.7  | Updating output grants                                                       |

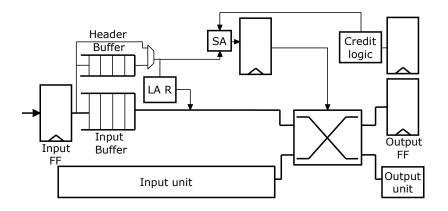

| 3.8  | A single-stage EB router                                                     |

| 3.9  | Buffered crossbar EB router                                                  |

| 3.10 | The interleaving deadlock cyclic dependency                                  |

| 3.11 | Using one subnetwork per traffic class                                       |

| 3.12 | Hybrid EB-CS network                                                         |

| 3.13 | Hybrid EB-VC router                                                          |

| 3.14 | The wormhole router                                                          |

| 3.15 | Two-stage hybrid EB-wormhole router                                          |

| 3.16 | Two-stage hybrid EB-wormhole router with input EBs                           |

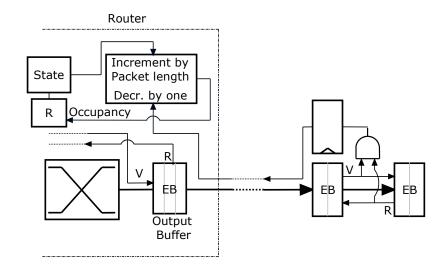

| 3.17 | Measuring output occupancy in EB networks                                    |

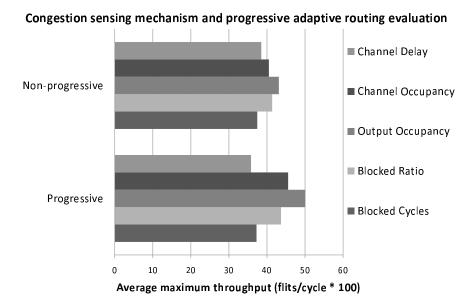

| 3.18 | elastic buffer (EB) network congestion sensing mechanism comparison          |

|      | using UGAL in a FBFly                                                        |

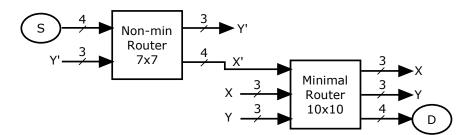

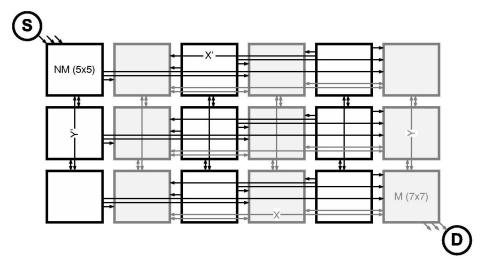

| 3.19 | The UGAL FBFly with EB flow control                                          |

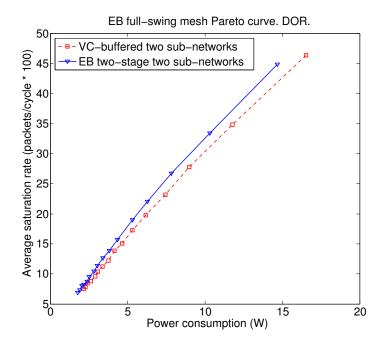

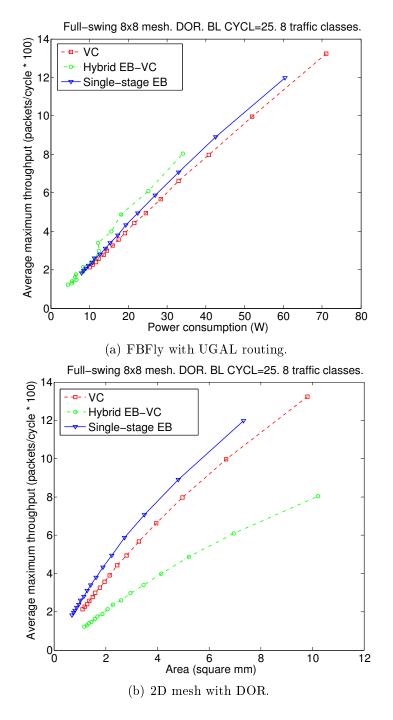

| 3.20 | Power-throughput Pareto-optimal curve for the mesh and full-swing            |

|      | channels                                                                     |

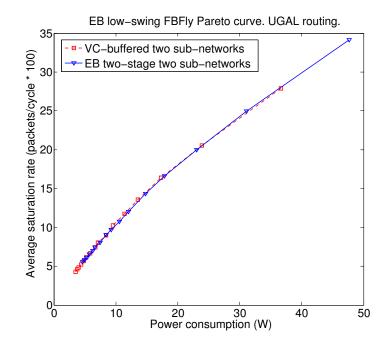

| 3.21 | Power-throughput Pareto-optimal curve for the FBFly and low-swing            |

|      | channels                                                                     |

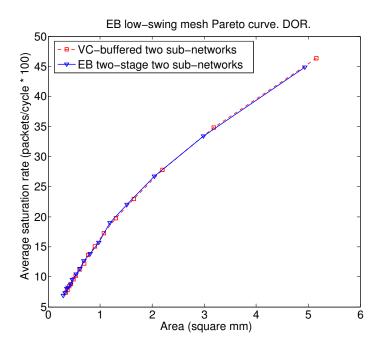

| 3.22 | Area-throughput Pareto-optimal curve for the mesh and low-swing              |

|      | channels                                                                     |

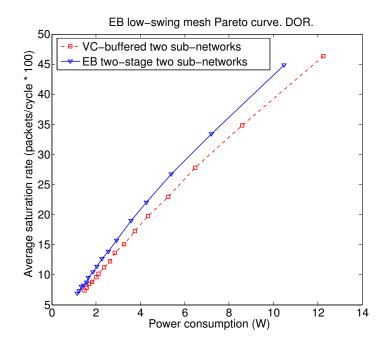

| 3.23 | Power-throughput Pareto-optimal curve for the mesh and low-swing             |

|      | channels                                                                     |

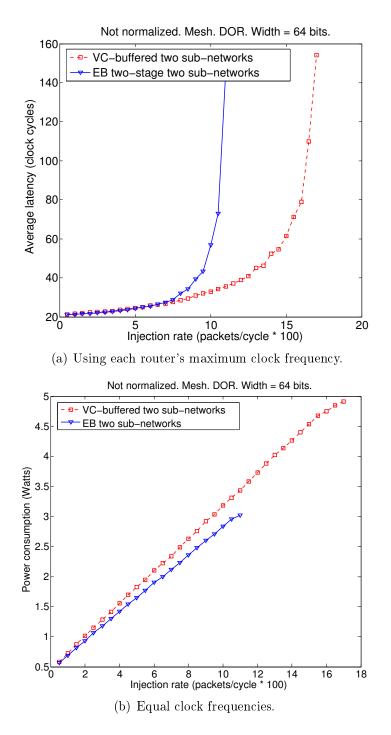

| 3.24 | Latency and power by increasing the injection rate for the $4 \times 4$ mesh |

|      | under uniform random traffic                                                 |

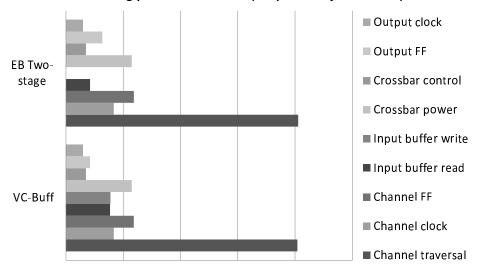

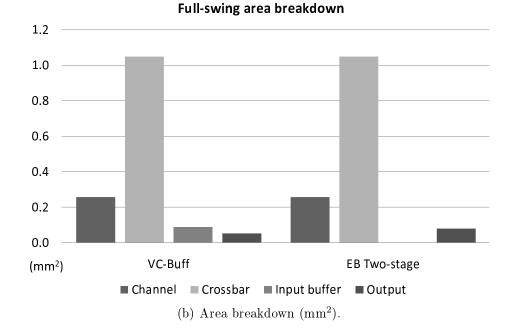

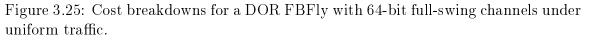

| 3.25 | Cost breakdowns for a DOR FBFly with 64-bit full-swing channels                 |     |

|------|---------------------------------------------------------------------------------|-----|

|      | under uniform traffic                                                           | 83  |

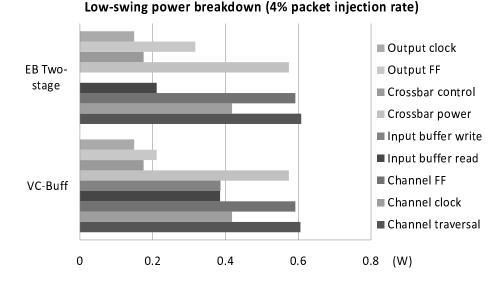

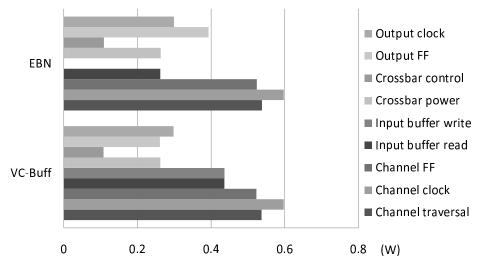

| 3.26 | Low-swing power breakdown. Same case as Figure 3.25                             | 84  |

| 3.27 | Low-swing power breakdown for the mesh                                          | 85  |

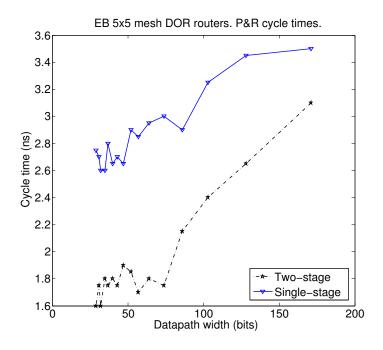

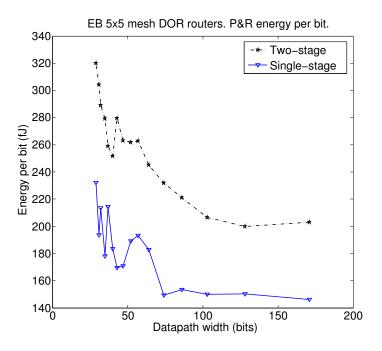

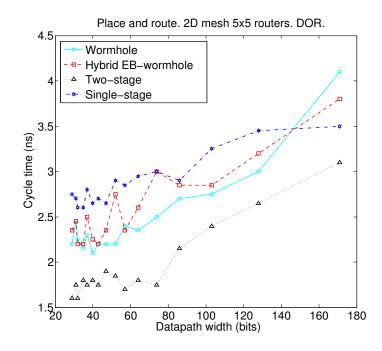

| 3.28 | EB router cycle time PnR implementation results                                 | 86  |

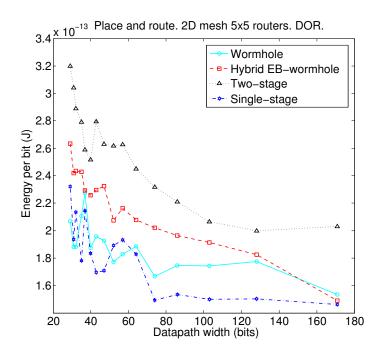

| 3.29 | EB router energy per bit PnR implementation results                             | 86  |

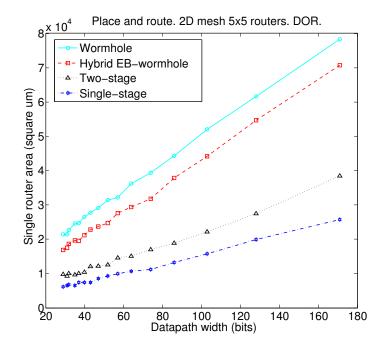

| 3.30 | EB router area PnR implementation results                                       | 87  |

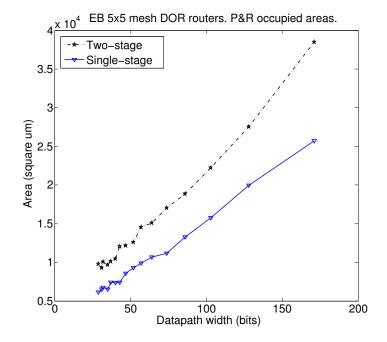

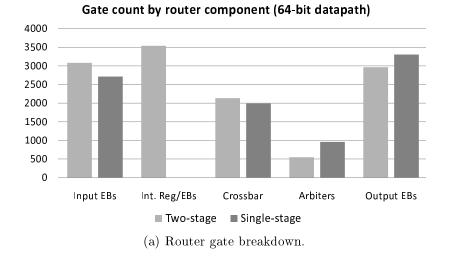

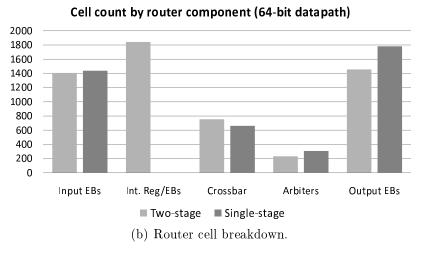

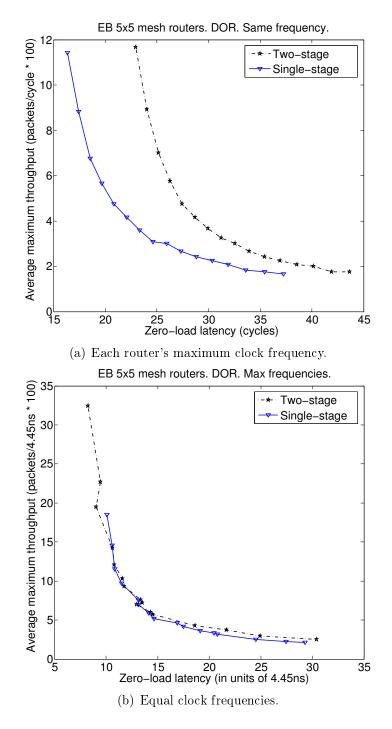

| 3.31 | Router PnR gate and cell breakdown                                              | 88  |

| 3.32 | EB router latency-throughput comparison                                         | 90  |

| 3.33 | Hybrid EB-VC Pareto-optimal curves.                                             | 92  |

| 3.34 | EB and wormhole routers cycle time after PnR. $\ldots$                          | 95  |

| 3.35 | EB and wormhole routers energy per transferred bit after PnR. $\ .$             | 95  |

| 3.36 | EB and wormhole routers occupied area after PnR. $\ldots$                       | 96  |

| 3.37 | Power and area breakdown after PnR. $\ldots$                                    | 97  |

| 3.38 | Injection rate vs. latency for EB and wormhole routers                          | 99  |

| 3.39 | Maximum throughput by traffic pattern for EB and wormhole routers.              | 100 |

| 3.40 | Injection vs. area for EB and wormhole routers                                  | 102 |

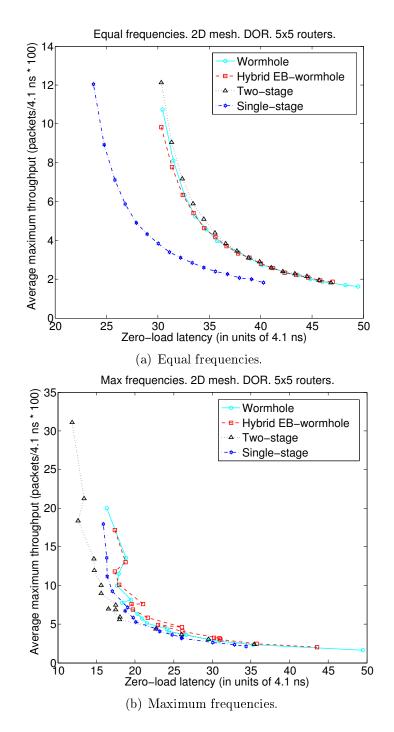

| 3.41 | Throughput vs. latency for EB and wormhole routers                              | 103 |

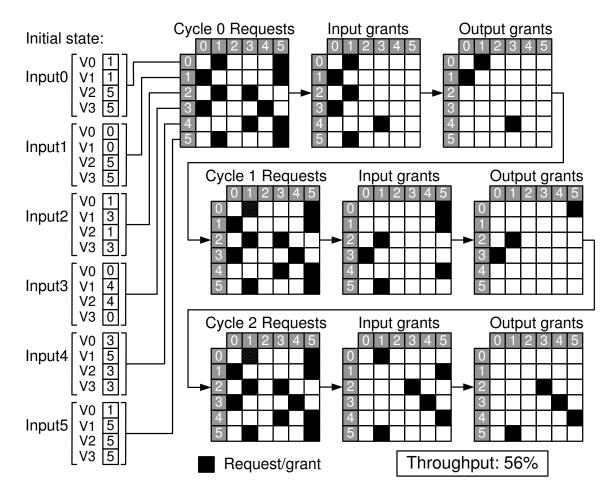

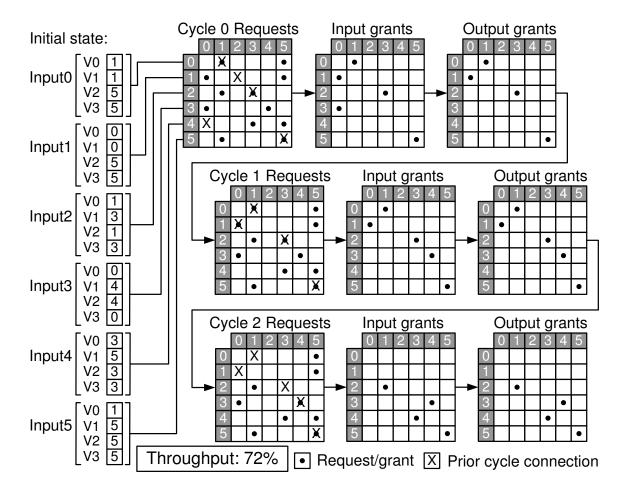

| 4.1  | Example allocation of iSLIP without packet chaining                             | 111 |

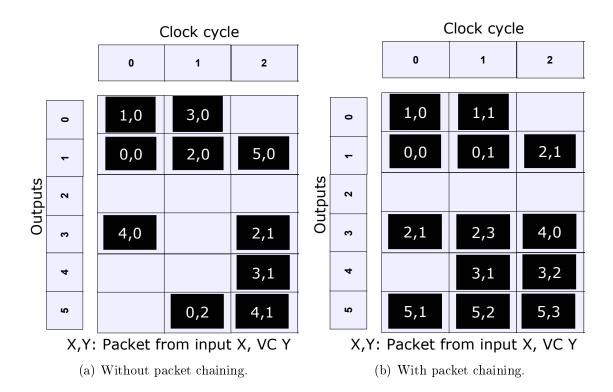

| 4.2  | Example allocation of iSLIP with packet chaining                                | 113 |

| 4.3  | A timeline of output port usage using the same example                          | 114 |

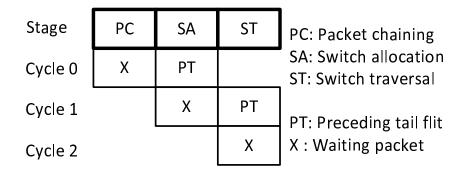

| 4.4  | An example of flit X being chained to use PT's connection                       | 118 |

| 4.5  | Increasing the injection rate beyond saturation illustrates network in-         |     |

|      | stability                                                                       | 123 |

| 4.6  | Comparison of packet chaining with other allocators. $\ldots$ $\ldots$ $\ldots$ | 125 |

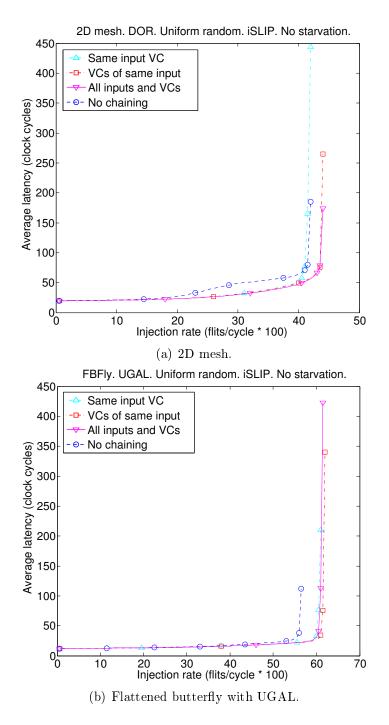

| 4.7  | Injection rate-throughput with single-flit packets                              | 128 |

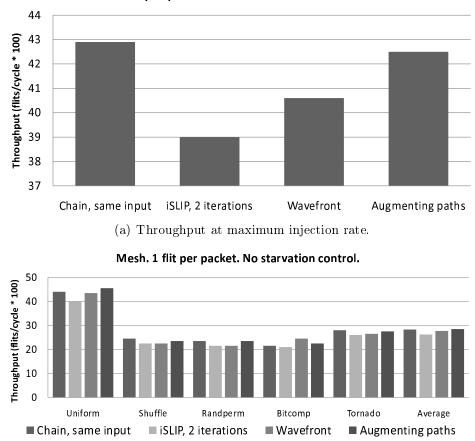

| 4.8  | Allocator comparison by traffic pattern                                         | 129 |

| 4.9  | Throughput by packet length in flits for the mesh                               | 131 |

| 4.10 | Throughput by packet length for the different allocators averaged across        |     |

|      | traffic patterns.                                                               | 132 |

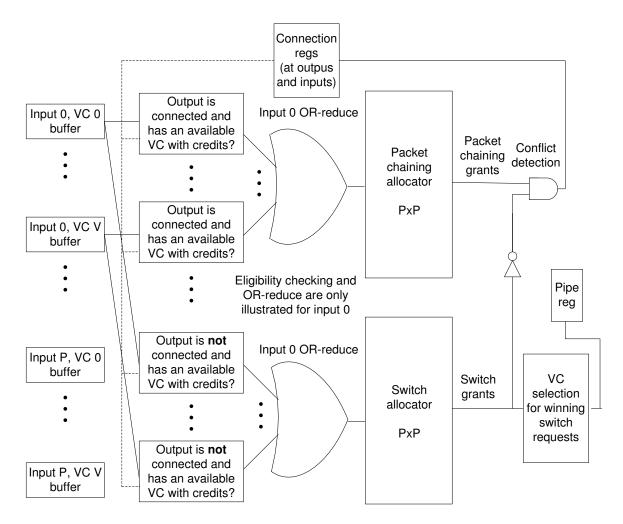

| 4.11 | An illustration of grants by the PC allocator.                     | 135 |

|------|--------------------------------------------------------------------|-----|

| 4.12 | Block diagram of the PC and SA stages with the PC and switch allo- |     |

|      | cators in parallel                                                 | 141 |

## Chapter 1

## Introduction

In recent years, computer architecture research has experienced a substantial shift in focus. Technology scaling has slowed down, which has led to scaling difficulties for large uniprocessors [91]. Some of these difficulties are that the clock frequency of today's large uniprocessors can not simply be increased, or the power dissipation will become prohibitive. In addition, uniprocessor performance scaling is further hindered because only a limited amount of parallelism can be extracted from a typical instruction stream using conventional superscalar instruction techniques [96, 67]. Despite these problems, applications such as large datacenters, social networking, computer graphics, gaming, machine learning, as well as scientific applications can benefit from additional processing power and thus motivate research to provide processing power beyond that made possible solely by uniprocessor scaling [47].

This has sparked the rise of parallel computing. Parallel computing divides any given problem into subproblems. Each subproblem is handled by a single processing unit in parallel with the rest. Parallel computing faces numerous challenges from the application level all the way down to the architecture and VLSI level [4]. From the hardware's perspective, parallel computing systems are limited by the area and power costs of adding more processing units, as well as by the need for the processing units to communicate with each other and the cache hierarchy. From a programmer's point of view, there are many crucial problems, such as parallel programming which includes parallelization of workloads, programming languages, task placement and scheduling, as well as communication patterns between processing units and tasks. Applications are often limited by their inherent lack of parallelism, which prevents them from taking advantage of all the processing units available to them.

There has been substantial research on parallel computing focusing on each of the important challenges. Large-scale chip multiprocessor (CMP) architectures have been developed to fill a processor die with multiple processing units. The processing units in a CMP can vary from simple in-order pipelines to moderately complex superscalar processing units. Even though in many systems using many simple processing units is more cost efficient than fewer complex ones [18, 19], design requirements and the inherent parallelism of the anticipated applications dictate the choice of processing units. CMPs can take full advantage of future technology scaling because they can always deploy more processing units, instead of making the existing ones more complex. An added benefit of multi-core systems is redundancy which can be used for error detection and correction, as well as the ability to power gate idle processing units while others perform computations [108].

Apart from processing units, CMPs also require cache blocks and other blocks (such as memory controllers). The majority of CMPs use private L1 caches attached to each processing unit. However, there have been numerous proposals for L2 caches that can be shared or private, and centralized or distributed across the chip [98, 114]. Each such block connects to an on-chip router through a network interface in order to communicate with other processing units, cache blocks, memory controllers or other units in order to facilitate communication for parallel workloads, task migration, and other functions. This is illustrated in Figure 1.1.

There have been multiple parallel programming languages or libraries for existing languages which provide programmers the ability to spawn threads to communicate via explicit message passing [101] or via sharing memory address space [53]. Past research on parallel computing not only addresses numerous shortcomings, but also highlights the importance of communication patterns, data placement and the network fabric, because the constant exchange of information requires energy, as well as is an important factor to performance [98, 102, 112]. These factors play a more important role in large-scale systems.

Figure 1.1: Abstract illustration of a multi-core architecture.

Small-scale CMPs have the option of using interconnect schemes such as buses, rings and crossbars [66, 24]. While buses are relatively simple, they suffer from performance scalability issues because all communication is serialized. Moreover, arbitration for the shared medium can take many cycles due to the propagation delay to and from the allocator. On the contrary, crossbars eliminate serialization by providing a separate path from each source to each destination. Unfortunately crossbars also do not scale because the area and power costs of a crossbar increase quadratically with the number of sources and destinations. Finally, rings have a large average hop count because it is proportional to the number of routers, and all traffic shares the same links, making bandwidth a potential bottleneck. Hence, none of these three interconnect options are appropriate for large-scale CMPs.

## 1.1 Overview of On-Chip Networks

### 1.1.1 Basic Architecture of On-Chip Networks

Packet-switched on-chip networks have been proposed as a scalable and modular communication medium for large-scale systems, such as CMPs [23, 27, 92]. On-chip

Figure 1.2: Architecture of a typical VC router.

networks are composed of a set of routers connected via point-to-point links in a manner specified by the network topology. Packets are divided into flow control digits (flits). Flits may be composed of multiple–but usually one–physical digits (phits); the size of phits is defined by the network datapath width. Large data flows are typically divided into multiple packets in order to aid resource allocation and routing in the network. With this organization, packets are transferred across the narrower channels over several cycles, incurring a serialization latency which is equal to the number of cycles to transmit the tail (last) flit after submitting the head (first) flit, in the absence of backpressure. The head flit carries the destination address that routers use to determine the proper output port and virtual channel (VC) [22] for the whole packet. Routing can be either deterministic (always follows the same path between any two points), oblivious (includes random choices) or adaptive (network stage such as congestion is taken into account).

Routers are the basic building blocks of scalable interconnects. Routers using VC flow control use per-VC input port buffers. Head flits at buffer heads go through routing computation and VC allocation. Non-head flits are assigned the same output port and VC as their head flit. Flits then proceed to switch allocation. Allocators try to find the best match considering all requests and output port states. Winning flits traverse the switching fabric, which delivers them to the proper output port. Routers are typically pipelined and several speculation or pre-computation techniques are used to reduce the critical path or the latency under low load [85, 59]. A typical VC router is illustrated in Figure 1.2.

Routers optimized for latency use look-ahead routing which performs the routing computation for the packet's next hop [32]. This way, packets enter the router with their outputs pre-encoded in the head flit. Thus, low-latency routers perform lookahead routing, VC allocation and switch allocation in the first pipeline stage and switch traversal in the second. To achieve this, speculative VC allocation is used which enables VC and switch allocations to be performed in parallel for all packets, but packets can only advance if they receive both grants [85]. Other routers use more pipeline stages to reduce complexity by removing speculation. This frequently shortens cycle time because it places VC allocation, switch allocation and perhaps routing into separate pipeline stages.

On-chip networks typically use VC flow control to enable deadlock avoidance, optimize channel utilization, improve performance and provide quality of service (QoS) [22, 13]. Disjoint traffic classes use separate VCs and routing algorithms which are designed to avoid cycles within and across VCs [29]. Blocked flits in one VC do not affect flits in other VCs since they are stored in separate FIFOs of each input's buffers. Per-VC credits are used to avoid input buffer overflow. A router can transmit a flit only if it has a credit to consume from the downstream router for that VC. Credits represent free slots in the corresponding next-hop buffer for that VC.

Figure 1.3: Two representative topologies in a 2D layout: 2D mesh (left) and 2D flattened butterfly (right).

#### 1.1.2 Topology

The topology defines how routers are connected to each other and to the network endpoints. For a large-scale system, the topology has a major impact on the performance and cost of the network. A variety of topologies have been used in on-chip networks [27, 13]. In this section, we discuss the 2D mesh and the 2D flattened butterfly (FBFly) [57] because they are used later in this thesis for performance evaluation. These topologies represent interesting design points since they offer distinct advantages and disadvantages and are fundamentally different. Figure 1.3 illustrates these topologies. Table 1.1 provides an asymptotic comparison of the two topologies for key metrics. Similar topologies exist to the ones we discuss in this section. For example, topologies which have direct links between distant routers (express links), such as express cubes [39, 25] or other low-diameter networks [113], can have similar advantages as the FBFly due to their reduced hop count. Finally, the fat tree topology [69] connects routers in a tree manner, and uses an increasing number of point-to-point links for routers closer to the root.

**2D mesh**. The 2D mesh is a popular topology choice in large-scale CMPs [11, 48]. Each of the  $\frac{T}{C}$  routers connects to its four neighboring routers and C source or destination nodes (network endpoints). The degree of concentration C, in nodes per router, is typically applied to reduce the number of routers and hops.

#### 1.1. OVERVIEW OF ON-CHIP NETWORKS

Table 1.1: Comparison of two popular topologies for a CMP system with T sources and destinations (cores, cache banks, and controllers). The point-to-point links have a width of W bits. N is the number of routers in the network and P is the number of input/output ports of each one. C refers to the concentration factor. The hop count is the number of link traversals under dimension-order minimal routing. The average number of hops assumes uniformly distributed traffic.

| Router   |    | s(N)          | Router 2 | I/Os (P)            | Bisecti         | on BW                                  |                 |

|----------|----|---------------|----------|---------------------|-----------------|----------------------------------------|-----------------|

| 2D mesh  |    | $\frac{T}{C}$ |          | $(C \cdot$          | + 4)            | $\sqrt{N}$                             | $\overline{N}W$ |

| 2D FBFly |    | $\frac{T}{C}$ |          | $(C+2(\sqrt{N}-1))$ |                 | $\sqrt{N}W\lfloor \frac{N}{2} \rfloor$ |                 |

|          |    |               | Hops     | (worst)             | Hops (av        | verage)                                |                 |

|          | 2D | mesh          | 2        | $2\sqrt{N}$         | $\sim \sqrt{N}$ | (7) + 1                                |                 |

|          | 2D | FBFly         |          | 4                   | 3.5             | 5                                      |                 |

A mesh topology with a concentration C of more than one is commonly referred to as a cmesh [40, 24].

The major advantage of the mesh is its simplicity. Links are short and balanced and the overall layout is very regular. The routers are low radix with up to C + 4 input and output ports, which reduces their area footprint, power overhead and critical path. The major disadvantage of the mesh is the large number of hops that flits have to potentially go through to reach their final destination; the number of hops is  $2\sqrt{N}$  for N routers (the hop count is the number of link traversals under dimension-order minimal routing). Each router imposes a minimum latency (e.g. 2 cycles for latency-optimized routers) and is a potential point of contention. A large number of hops has direct impact on the energy consumed in the interconnect for buffering, transmission, and control, Hence, meshes could face performance and power scalability issues for largescale systems. To address these concerns, researchers have proposes meshes with physical [25] or virtual [65] express links.

2D Flattened Butterfly. The 2D FBFly is derived by flattening the routers in

each row of a conventional butterfly topology while preserving inter-router connections [57]. This way, routers connect with every other router in each axis. Essentially, this topology provides the connectivity of a mesh with additional express links. Thus, in a  $4 \times 4$  network, each router connects with three other routers in the X axis, and with three other routers in the Y axis. Similarly to the mesh, a concentration factor is typically applied to reduce the router overhead. If the concentration factor in our example is four nodes per router, each router is  $10 \times 10$ .

The major advantage of the FBFly is the small number of hops for network traversals under minimal routing. For two dimensions, flits can always reach any destination node with four hops (i.e. three routers). Using the longer links minimizes the number of routers visited and their associated latency and energy overheads. The additional links reduce the chance of congestion and provide higher bandwidth as well. The major disadvantage of the FBFly is the need for high-radix routers, which are expensive in terms of area and power due to the large switches they require. The larger number of links also increases area and leakage power.

## 1.2 On-Chip Network Consumption and Motivation

Current and past on-chip network research shares the common goal of reducing power consumption compared to that of the *ideal interconnect*. The ideal interconnect represents an abstract network where the only power consumed is that for propagation between senders and receivers. This does not include any of the overhead present in realistic networks, such as buffers, allocators and switches, which were added for the purpose of providing a functionally correct network, and perhaps provide additional services such as QoS. Because such overhead is necessary, realistic implementations aim to reduce the gap, illustrated in Figure 1.4 and originally presented in [65], but can never fully close it. Much of the complexity of past proposals to reduce energy stems from the fact that such techniques must also respect other constraints of the network, such as cycle time, area and latency. Thus, optimizing for power tends to

Figure 1.4: The power consumption gap between realistic on-chip networks and the ideal interconnect which only consumes power for data propagation.

focus on increasing throughput per unit of power, while also respecting the other constraints.

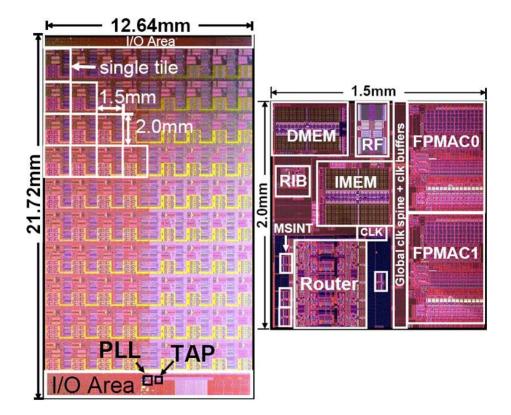

Recently, Intel produced the Teraflop processor, with 80 single-precision, floatingpoint cores [48]. This design delivers performance in excess of teraflops and to a large degree was an attempt to identify shortcomings of current architectures in preparation for future many-core designs. The Intel 80-core Teraflop processor is organized in tiles. Each tile contains instruction and data memory slices, computation blocks and an on-chip router. The floorplan of the design is illustrated in Figure 1.5.

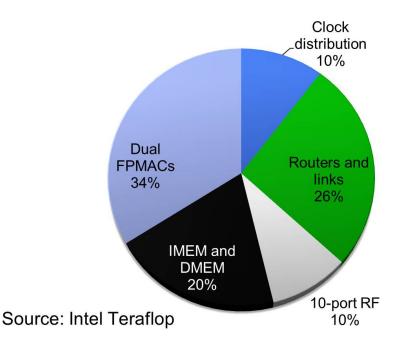

The Intel 80-core Teraflop processor features a 2D mesh to interconnect tiles. Routers are clocked at 5GHz, and the network is mesochronous (the clock frequency is the same throughout the design, but the clocks of adjacent clock regions need not be phase-aligned). Because of the long channels, high frequencies and high computational demands, the on-chip network consumes 26% of each tile's power, as illustrated in Figure 1.6. The rest of the power is consumed predominantly by clocking due to the high frequencies, and by the expensive floating point operations. This served as another confirmation to the on-chip network community of the importance of reducing the energy consumption of on-chip networks especially when considering larger-scale systems. Other studies have reached similar conclusions by reporting that instruction and data supply comprise 70% of the power for a RISC processor, compared to 5% for the processor datapath [5].

Figure 1.5: Overview of the Intel 80-core Teraflop processor.

Figure 1.6: Power breakdown of a single tile in the Intel 80-core Teraflop processor.

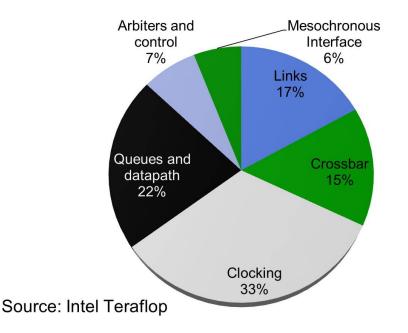

Figure 1.7 illustrates the power breakdown of the on-chip network in the Intel 80core Teraflop processor. All the components illustrated offer numerous opportunities for optimizations and have sparked research from custom circuit design to routing and flow control. However, the only component which is not fundamentally required and can thus be removed completely is the router buffers, which represents 22% of the network power. Channels are necessary to data and control information propagation. Crossbars are required to allow packets take turns and thus cannot be removed in a packet-switched network. Finally, allocation and routing logic is necessary for the correct operation of crossbars and packet movement in packet-switched networks. This has motivated research to eliminate router buffers.

Router buffers are used to handle contention. However, contention can be prevented or handled in other ways. Circuit-switched networks prevent contention by pre-allocating bandwidth [24]. However, circuit-switched networks impose large latency and power overheads because circuits need to be established before packet transmission, even for small packets. Bufferless networks handle contention by dropping

Figure 1.7: Network power breakdown in the Intel 80-core Teraflop processor.

packets under contention and relying on the source to retransmit them, or deflecting them to any free output. Since bufferless flow control does not have the cost and timing overhead of router buffers which has been shown to be significant, bufferless flow control has been researched recently as a way to reduce the energy of on-chip networks [83, 30].

### 1.3 Thesis Overview

In this thesis, we perform a comprehensive study to improve and evaluate bufferless flow control as a viable solution to the rising router buffer costs. To avoid the complications and complexity of bufferless flow control illustrated in our study, this thesis proposes elastic buffer (EB) flow control which provides buffering in the network without the timing and cost overhead of router buffers. Finally, this thesis proposes packet chaining which increases the matching quality of switch allocators to be comparable or superior to more complex and slower allocators. Our bufferless study is presented in Chapter 2; it focuses on deflection networks and starts by improving routing in deflection networks. For this, we propose multidimensional routing (MDR) which defines all outputs which reduce the distance of packets to their destination as *productive*, instead of only the output according to dimension-order routing (DOR). This way, deflection becomes less probable because there are more productive outputs. This reduces latency by an average of 5% compared to BLESS [83], which describes a deflection flow control scheme we use for our comparisons. Furthermore, we synthesize a switch allocator required by deflection flow control, and show that because flits cannot wait in inputs, all inputs must receive a grant to an output, and thus the allocator has a long serial path that traverses every output arbiter. Deflection allocators also need to prioritize older packets to prevent livelocks. Therefore, deflection switch allocators have an 81% longer delay than switch allocators for a VC network with two VCs.

In addition, our bufferless study examines closely the implementation and usage of input buffers. Not only can input buffers be implemented efficiently with custom SRAM blocks [6], but empty buffers can be bypassed in the absence of contention such that dynamic energy is not consumed when not necessary [107]. This way, power savings for the bufferless network are marginal at best. Since one deflection induces two extra hops, deflections consume  $6.7 \times$  the dynamic energy for buffering contending flits instead. Specifically, the deflection network only consumes less power than the buffered network for injection rates lower than 7%, but never consumes less power than 98.7% of the power for a 2D mesh buffered network. That is because at low loads leakage power provides a marginal advantage to bufferless networks. On the contrary, increasing the injection rate increases the number of deflections, which increases the channel activity factor by 4.6% at an injection rate of 20%, which equals  $5.5\times$  the buffer access and leakage power. Moreover, because each deflection causes an even number of hops, the maximum latency for BLESS is 108 cycles with an injection rate of 20%, whereas for the buffered network it is 13. The buffered network also has a 17% lower average latency. Moreover, the VC network provides 21% more throughput per unit power. Finally, bufferless networks need large buffers at the endpoints to prevent protocol deadlocks and buffer overflow due to the lack of backpressure.

To retain buffering in the network without the cost for router buffers and without the complications and complexity of bufferless flow control, we propose EB flow control in Chapter 3. EB flow control adds a simple control logic block to drive the enable inputs of the master and slave latches of master-slave pipeline flip-flops (FFs) separately. This allows FFs to use each latch independently for buffering and makes FFs behave as two-slot FIFOs (EBs). Consecutive EBs make network channels act as distributed FIFOs. Flits advance to the next EB using a ready-valid handshake. With EB flow control, channels are used for buffering in lieu of input buffers.

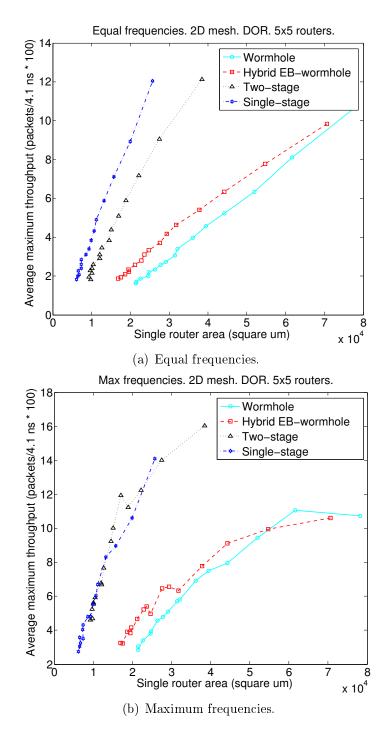

Removing input buffers removes VCs. This increases head-of-line blocking and therefore reduces performance. However, area and power are also reduced from removing the buffers. Therefore, the datapath can be made wider such that performance or cost is equalized compared to a network with input buffers. Removing VCs also removes the VC allocator. Consequently, because an input may only request a single output, the switch allocator is replaced by output arbiters. Furthermore, credits are not used. Therefore, routers are significantly simplified compared to VC routers [85]. However, due to the lack of credits, EB networks use a congestion sensing mechanism which counts flits bidding for and traversing output channels.

Two EB router designs are presented. The two-stage EB router emphasizes on throughput by reducing cycle time. Compared to a VC router with speculative switch allocation [85], the two-stage EB router offers 8% more throughput per unit power in a 2D mesh with DOR, assuming equal clock frequencies. It also reduces cycle time by 45%. The second EB router design merges the two-stages of the two-stage router to avoid pipelining overhead and prioritize latency. Compared to the two-stage router, this single-stage router requires 29% less energy per transferred bit but also has a 33% longer cycle time. By using the optimal EB router and shortest cycle time for each comparison, a 2D mesh EB network provides 21% more throughput per unit power, 22% more throughput per unit area or has an up to 45% shorter cycle time compared to a similar VC network. Furthermore, because EB networks have a wider datapath when equalizing performance or cost, they reduce zero-load latency.

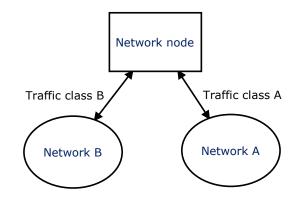

To provide complete traffic separation, multiple *physical channels are used in the* same way as multiple virtual channels (VCs). An efficient way to provide multiple physical channels is by using duplicate and independent physical networks. However, this is only efficient up to a number of traffic classes. To provide an arbitrarily large number of traffic classes, we propose a hybrid EB-VC router which reinstates input buffers with VCs but only to drain flits at router inputs that are blocked for a predefined number of cycles, as well as other flits belonging to the same class. Transmission of further flits of that class is hindered by a control signal routed upstream.

A properly-chosen predefined threshold makes hybrid EB-VC routers more energy efficient than VC routers because buffers are not used in the common case, as well as more energy efficient than EB routers because hybrid routers reduce head-of-line blocking (in addition to resolving deadlocks). Specifically, in a 2D mesh, networks with EB-VC routers offer 21% more throughput per unit power than VC routers, and 12% than EB routers. However, the presence of buffers as well as VC and switch allocators makes hybrid routers comparable to VC routers in area and cycle time. Even though area is comparable, hybrid routers still allow limited interaction between flits in different VCs. Thus, VC networks offer 41% more throughput per unit area compared to hybrid EB-VC networks, while EB networks offer 49%.

Cycle time can be crucial for network performance. However, VC and hybrid EB-VC networks require allocators to assign VCs to packets and permit them to traverse the switch [22, 85]. Because allocators are often in the router's critical path and the network is sensitive to allocator performance, there is a tradeoff between allocation quality and cycle time. To increase allocation quality without extending cycle time, in Chapter 4 we propose *packet chaining*, a method for improving allocation efficiency for iterative allocators that is particularly suited to networks with short packets and short cycle times.

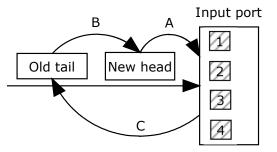

Packet chaining chains packets together, facilitating reuse of a departing packet's switch connection. Connections are established when head flits are granted by the switch allocator, as in incremental allocation [84]. This way, a collection of short packets destined to the same output keep resources reserved in the switch allocator similar to longer packets. This allows an allocator to build up an efficient matching over a number of cycles like incremental allocation, but not limited by packet length.

Packet chaining includes starvation control because connections could otherwise remain active indefinitely.

Packet chaining is implemented by adding a separate packet chaining (PC) allocator, and thus doubles the area and power for allocation. The allocation timing path is lengthened only marginally, since the PC and switch allocators operate in parallel. Packet chaining increases the allocation efficiency of a single-iteration separable allocator to be comparable to or higher than more expensive and slower allocators. For single-flit packets at maximum injection rate, packet chaining increases network throughput by 15% and reduces average latency by 22.5%, compared to a highly-tuned router with incremental allocation using a single-iteration iSLIP switch allocator [74]. Packet chaining also outperforms multi-iteration iSLIP allocators and wavefront allocators [103] by 10% and 6% respectively, and gives comparable throughput with an augmenting path allocator [31]. Performance gains decrease as packet length increases because incremental allocation creates connections as well. However, packet chaining still provides better or comparable throughput with more expensive and slower allocators for packets of any length. Finally, packet chaining increases IPC up to 46%(16% average) for a CMP executing application benchmarks, because short packets are critical in typical cache-coherent CMPs.

### **1.4** Thesis Contributions

This thesis makes the following contributions:

- We conduct a comprehensive evaluation of bufferless flow control, focusing on deflection flow control. In this study, we first optimize routing in bufferless networks and then show the complications and complexity of bufferless flow control. Thus, we conclude that bufferless flow control is not a viable technique to remove router buffers and consequently their cost and timing overhead.

- To provide buffering in the network without the cost for router buffers we propose EB flow control. We describe the single-stage EB router which focuses on reducing latency and the two-stage EB router which minimizes cycle time. For

also propose a congestion-sensing mechanism to be used instead of credit count. Traffic separation is provided with separate independent networks. However, for a large number of traffic classes, we propose the hybrid EB-VC router which can handle an arbitrary amount of traffic classes and also increases throughput per unit area compared to both VC and EB networks.

• We propose packet chaining which increases the matching quality of iterative allocators to be comparable or superior to more complex and slower allocators. Packet chaining is an elegant solution to the tradeoff between matching quality and cycle time, and focuses on single-flit packets which are critical in typical cache-coherent CMPs.

## 1.5 Thesis Structure

The rest of this thesis is structured as follows: Chapter 2 presents our study which illustrates the complications of bufferless flow control. Chapter 3 presents elastic buffer flow control which provides buffering to the network without the cost for router buffers. Chapter 4 presents packet chaining which increases allocation quality without increasing cycle time. Chapter 5 discusses related work. Finally, Chapter 6 concludes and provides future research directions.

## Chapter 2

## **Bufferless Flow Control**

This chapter examines if bufferless networks are an efficient alternative to buffered networks [81]. This is done by comparing a state-of-the-art packet-switched bufferless network with deflecting flow control, BLESS [83], and the currently-dominant virtual channel (VC) buffered flow control [22]. To perform an equitable comparison, both networks are optimized. In particular, VC networks feature efficient custom SRAM buffers and empty buffer bypassing. This chapter also proposes multi-dimensional routing (MDR), a novel routing scheme for BLESS, where flits bid for all outputs that would reduce their distance to their destinations regardless of dimension order constraints. As shown in this chapter, bufferless networks offer a minimal energy advantage at best, while offering lower throughput and facing complications such as allocation time and latency distribution. Therefore, bufferless flow control is not a viable solution to the rising router buffer costs.

Bufferless flow control aims to reduce on-chip network cost and timing overhead by removing the router buffers, which are often reported to consume significant amounts of area and power. Specifically, bufferless flow control proposals report up to 60% area and up to 39% energy savings in a conventional CMP network [83]). Other cost models and buffer implementations quote numbers for the buffers as high as 75% [37] of the router area and 22% [54] of the router energy. Finally, recent designs from Intel consume 28% of the chip energy in the on-chip network, and 22% of the router power in the buffers [48].

The cost of router buffers has motivated research to decrease it. This research focuses both on buffer implementation and usage. Network designers have to choose between custom SRAMs, compiler-generated SRAMs, and flip-flop (FF) or latch arrays. While buffer implementation is a tradeoff of engineer time and cost, custom SRAMs can significantly reduce implementation costs. Research on buffer usage has proposed schemes to use buffer space more efficiently, thus reducing buffer size or dynamic power. These optimizations may reduce buffering overhead up to a point where the extra complexity and performance issues of bufferless flow control outweigh potential cost savings. Related work is analyzed in Section 5.

### 2.1 Methodology

To perform the evaluations, we use a modified version of Booksim [24] for cycleaccurate microarchitecture-level network simulation. To estimate area and power we use ITRS predictions for a 32nm high-performance process [50], operating at 70°C. Modeling buffer costs accurately is fundamental in our study. Orion [106] is the standard modeling tool in network-on-chip (NoC) studies, but recent studies show that it can lead to large errors [54, 55], and the update fixing these issues was not available at the time of this work. Instead, the models from Balfour and Dally [6] are used, which are derived from basic principles, and validate SRAM models using HSPICE.

The network is assumed to be clocked at 2GHz with 512-bit packets. Channel wires are routed above other logic and include only repeater and flip-flop area in channel area. The number and size of repeaters per wire segment are chosen to minimize energy. The conservative low-swing model of this chapter has 30% of the full-swing repeated wire traversal power and twice the channel area [45]. Router area is estimated using detailed floorplans. VC buffers use efficient custom SRAM-based buffers. We do not use area and power models for the allocators, but perform a detailed comparison by synthesizing them. Synthesis is performed using Synopsys Design Compiler and a low-power commercial 45nm library under worst-case conditions. Place and route is done using Cadence Silicon Encounter. Local clock gating

is enabled.

Evaluation comparisons use FLIT-BLESS. FLIT-BLESS performs better than WORM-BLESS [83], but incurs extra overhead because all flits contain routing information. However, this overhead is not modelled in this chapter, giving BLESS a small advantage over buffered flow control. Furthermore, buffered BLESS has not been evaluated in [83], and therefore is not considered in our study.

Two topologies are used for a single physical network with 64 terminals. The first is an  $8 \times 8$  2D mesh with single-cycle channels. Routers are  $5 \times 5$  and have one terminal connected to them. The second is a 2D flattened butterfly (FBFly) [57] with four terminals connected to each router. Therefore, there are 16 10×10 routers laid out on a 4×4 grid. Short, medium and long channels are two, four and six clock cycles long, respectively. Injection and ejection channels are a single cycle long. For both topologies, one clock cycle corresponds to a physical length of 2 mm. These channel lengths are chosen so that both networks cover an area of about 200 mm<sup>2</sup>.

Routers use a two-stage pipeline. The VC network features input-first separable round-robin allocators, speculative switch allocation [95] and input buffer bypassing [107]. No communication protocol is assumed. The VC network uses dimensionorder routing (DOR) for the mesh and FBFly. The deflection network uses multidimensional routing, explained in Section 2.2. We do not assume adaptive routing for the VC network since such a comparison would require adaptive routing for the bufferless network as well. We choose the number of VCs and buffer slots to maximize throughput per unit power. While this penalizes the VC network in area efficiency, power is usually the primary constraint.

We generate results for either uniform random traffic or we average over a set of traffic patterns: uniform random, random permutation, shuffle, bit complement, tornado and neighbor [24]. This set is extended for the FBFly to include transpose and a traffic pattern that illustrates the effects of adversarial traffic for networks with a concentration factor. Averaging among traffic patterns makes our results less sensitive to effects caused by specific traffic patterns.

### 2.2 Routing in Bufferless Networks

BLESS networks use DOR [83]. In VC networks, DOR prevents cyclic network dependencies without extra VCs. Since flits are forced to complete their traversals in one dimension first, there can never be a flit wanting to turn from the last dimension back to the first one. However, in bufferless networks flits never block waiting for router buffers, so there can be no network deadlocks due to cyclic dependencies, making DOR unnecessary. As discussed in Section 2.4.4, extra care must be taken to prevent deadlocks arising from ejection buffers at network destinations, such as protocol deadlocks [42].

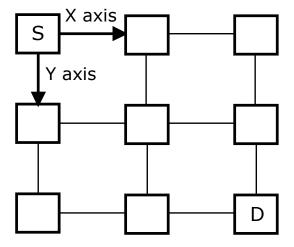

Two oblivious routing algorithms that decrease deflection probability are proposed here, based on the observation that a flit often has several *productive* outputs (i.e. outputs that would get the flit closer to its destination). For example, in a 2D mesh, those are the two outputs shown in Figure 2.1(a), unless the flit is already at one of the axes of its final destination. Our first routing algorithm, MDR, *exploits choice* by having flits request all of their productive outputs. If both outputs are available, the switch allocator assigns one pseudorandomly. However, this may make flits favor one dimension until there are no more hops in that dimension. Thus, flits will be forced to switch dimensions. During that time, they will have only one productive output, increasing their deflection probability.

With MDR, there is one productive output in each dimension with remaining hops. If a flit exhausts all hops in a dimension, it will have one less productive output, increasing its deflection probability. We can improve MDR by prioritizing the dimension that has the most remaining hops, which increases the number of productive outputs at subsequent hops. We call this scheme prioritized multi-dimensional routing (PMDR). Figure 2.1(b) shows an example path with PMDR in a 2D mesh. Due to PMDR, all the hops except the last one have two productive outputs. In an FBFly with minimal routing, flits only take one hop in each dimension, so PMDR is equivalent to MDR. However, PMDR increases allocator complexity: since a BLESS allocator already needs to prioritize flits by age, PMDR requires either prioritizing output ports or two allocation iterations.

(a) MDR requests all productive outputs at each hop.

(b) PMDR prioritizes the output with the most hops remaining in that dimension.

Figure 2.2: Comparison of DOR, MDR and PMDR routing algorithms.

Figure 2.2 compares DOR, MDR and PMDR in mesh and FBFly bufferless networks. In the mesh, MDR offers 5% lower average latency than DOR and equal maximum throughput. In the FBFly, MDR achieves 2% lower average latency and 3% higher maximum throughput under uniform random traffic as well as the average over the set of traffic patterns. On the other hand, latency is decreased by 5% for the mesh and 2% for the FBFly, by average over all injection rates, under uniform random traffic. Under a sample 20% flit injection rate, 13% more flits were only able to choose a single output with DOR compared to MDR. Also, PMDR achieves only marginal improvements over MDR (0.5% lower average latency in the mesh). Given its higher allocator complexity, we use MDR for the rest of the evaluation.

## 2.3 Router Microarchitecture

This subsection explores router microarchitecture issues pertinent to bufferless networks.

### 2.3.1 Allocator Complexity

To conduct the analysis, this section presents an implementation of an age-based BLESS allocator, shown in Figure 2.3. Requests are partially ordered according to their age by the sorting blocks shown on the left, each of which sorts two requests. Partial ordering is guaranteed to detect the oldest flit, which is sufficient to prevent livelocks. In order to reduce the complexity and shorten the timing path of the sorting logic, our implementation does not generate a complete ordering of flits by age. Requests are assigned priority based on the result of the partial sort, with the oldest flit having the highest priority. The output arbiters satisfy the highestpriority request from those remaining, and then forward remaining requests to the next arbiter. Because the oldest flit has the highest priority, it is guaranteed to not be deflected, thus preventing livelocks.

Although the logic of each arbiter is simple, all requests need to be granted [83] because all flits need to be routed due to the lack of buffers. This creates a long critical

Figure 2.3: BLESS allocator implementation.

Figure 2.4: Empty buffer bypassing.

path that passes through each output. This critical path is necessary for deflection flow control, because the decision of a particular output arbiter may depend on the decision of other arbiters, because a flit that was not granted by other arbiters needs to be granted by that particular output. This critical path scales linearly with router radix. Note that this design would perform slightly worse than the idealized BLESS allocator that we use in our simulation-based evaluation. While the idealized BLESS allocator performs optimal matchings, the implementation described in this section trades off accuracy for cycle time. Therefore, BLESS is given an advantage by using an ideal allocator without considering timing and cost overheads.

Table 2.1 compares our BLESS allocator and an input-first separable speculative switch allocator with round-robin arbiters for a VC network with 2 VCs [10]. Dynamic power is estimated by applying Synopsys Design Compiler's default activity factor to all inputs. The VC network switch allocator represents a reasonable design and has comparable cycle time to other separable and wavefront allocators [10, 24]. We compare against the switch allocator because a similar VC allocator has a shorter

| Aspect             | Separable Input-First | Age-based | Delta |

|--------------------|-----------------------|-----------|-------|

| Number of nets     | 1165                  | 1129      | 0%    |

| Number of cells    | 1100                  | 1050      | 0%    |

| Area $(\mu m^2)$   | 2379                  | 2001      | -16%  |

| Cycle time (ns)    | 1.6                   | 2.9       | +81%  |

| Dynamic power (mW) | 0.48                  | 0.27      | -44%  |

Table 2.1: Allocator synthesis comparison.

critical path and speculation parallelizes VC and switch allocation [10].

As Table 2.1 shows, the age-based allocator has an 81% larger delay. If the allocator is on the router's critical path, this will either degrade network frequency or increase zero-load latency if the allocator is pipelined. The separable allocator need to maintain state in FFs for the round-robin arbitration. Therefore, it requires more area and power for the FFs and the associated clock tree. However, the area and power differences are a small fraction of the overall router area and power, which are dominated by the buffers and the switch [54, 6]. Therefore, it is unrealistic to assume bufferless routers with one pipeline stage, assuming a tight timing budget. Speculation is not applicable to reduce router latency in bufferless networks because there is only one type of allocation (switch) and flits failing speculation need to be deflected.

### 2.3.2 Buffer Cost

The cost models of this study assume efficient custom SRAM blocks for buffers [6], which impose a smaller overhead compared to other implementation options. However, designers might be unable to use such designs, e.g. due to process library constraints. Using either standard-size SRAM blocks or FF arrays will likely make buffers more costly, increasing the motivation for eliminating them or reducing their size. Additionally, we use empty buffer bypassing [107], shown in Figure 2.4. This allows flits to bypass empty buffers in the absence of contention. Empty buffer bypassing requires the addition of a FF to store flits which bypass the buffers, as well as a multiplexer to select among that FF and the buffer to feed the switch. Empty buffer bypassing has a negligible effect in timing and cost, but is able to drastically reduce the buffer dynamic power under light to medium load. Flits that bypass the buffer traverse that additional FF instead of the buffer, and therefore consume the energy to traverse one FF which is similar to traversing the pipeline FF of a two-stage bufferless router.

While these schemes suffice to implement efficient buffers, additional techniques could be applied. For instance, leakage-aware buffers [88] reduce leakage by directing incoming flits to the least leaky buffer slots and supply-gating unused slots. Also, to increase buffer utilization and reduce buffer size, researchers have proposed dynamic buffer allocation which makes more efficient use of buffer space, thus enabling a reduction in buffer size while maintaining performance constant [87].

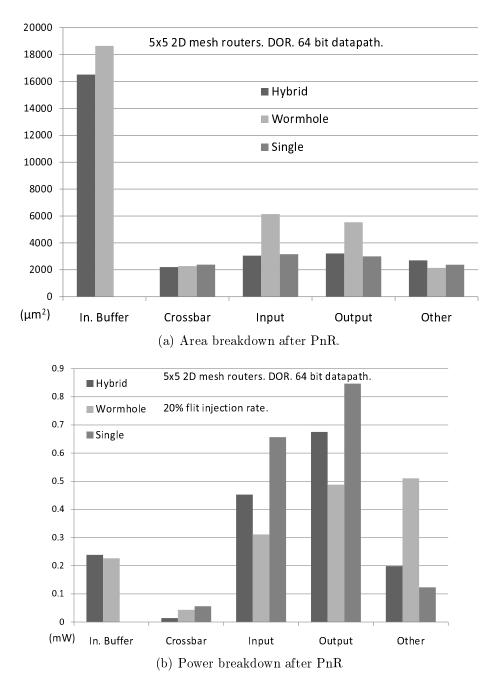

To check the accuracy of our models, we synthesized and then placed and routed a  $5 \times 5$  mesh VC router with 2 VCs and 8 buffer slots per VC. Due to process library constraints, we were only able to use FF arrays for buffers. With this implementation, the FF arrays occupied 62% of the overall router area and consumed 18% of the router power at a 20% flit injection rate with uniform random traffic. A compiler-generated SRAM block from the same library would occupy 13% of the router area. The SRAM area results are in line with our models.

### 2.4 Evaluation

This subsection presents a quantitative comparison of BLESS and VC flow control and discusses design tradeoffs.

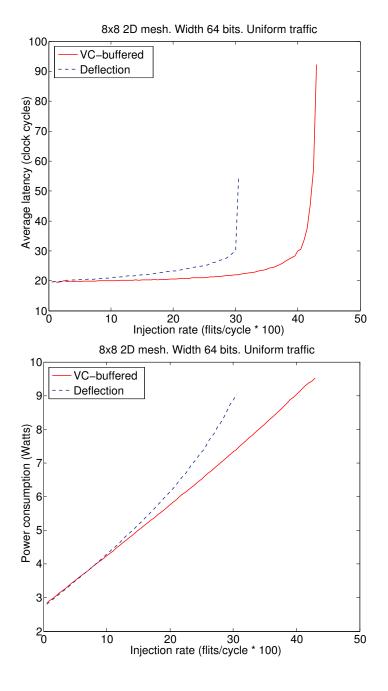

Figure 2.5: Mesh latency and power comparison.

Figure 2.6: FBFly latency and power comparison.

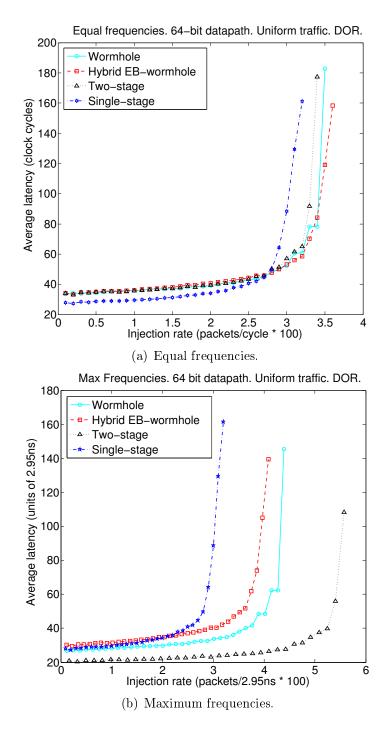

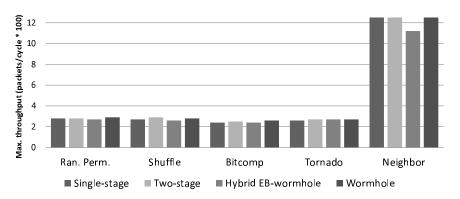

#### 2.4.1 Latency and Throughput

Figure 2.5 and Figure 2.6 present latency and power as a function of flit injection rate. VC routers are optimized for throughput per unit power. They have 6 VCs with 9 buffer slots per VC in the mesh, and 10 slots per VC in the FBFly. The VC network has a 12% lower latency for the mesh on average across injection rates that do not saturate either network, and 8% lower for the FBFly. At a sample 20% flit injection rate, the VC network has a 17% lower latency for the mesh, and 10% lower for the FBFly. Also, the VC network provides a 41% higher throughput for the mesh, and 96% higher for the FBFly. If we average over the set of traffic patterns, the VC network provides a 24% and 15% higher throughput for the mesh and FBFly, respectively.

Deflecting flits increases the average hop count and therefore the average channel activity factor for a given injection rate. The impact of this effect depends on the injection rate and is shown by the increase in dynamic power in the deflection network due to the larger activity factor. Specifically, the deflection network consumes more power than the buffered network for flit injection rates higher than 7% for the mesh and 5% for the FBFly. For lower injection rates, buffer power is higher than the power consumed by deflections. However, even then the deflection network never consumes less power than 98.7% of the VC network power for the mesh, and 98.9% for the FBFly. The higher power in VC networks is mainly due to buffer leakage.

These small power gains are outweighed by the allocator complexity and the other issues discussed in this paper. Furthermore, if a network always operates at such low injection rates, it is likely overdesigned because the datapath width need not be this wide, making the network more expensive than necessary. In other words, a buffered network that is made cheaper by narrowing its datapath is a more cost-efficient choice over a bufferless network with wide channels.

Without empty buffer bypassing, the dynamic buffer power increases significantly, as detailed in Section 2.4.2. In this case, the deflection network consumes less power for flit injection rates lower than 17% for the mesh, and 12.5% for the FBFly. A power-injection rate curve for the mesh is shown in Figure 2.11. This emphasizes the importance of buffer bypassing.

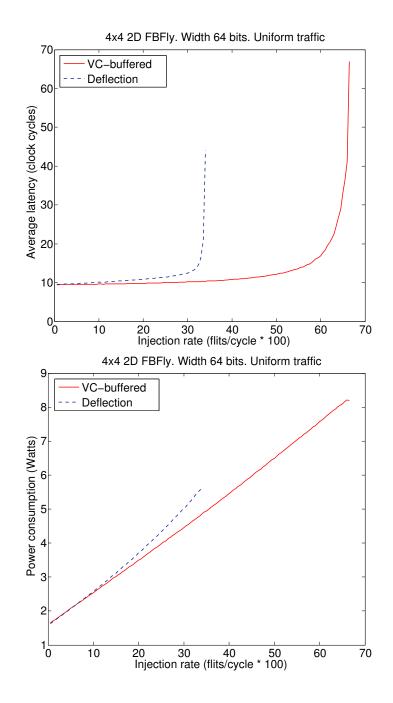

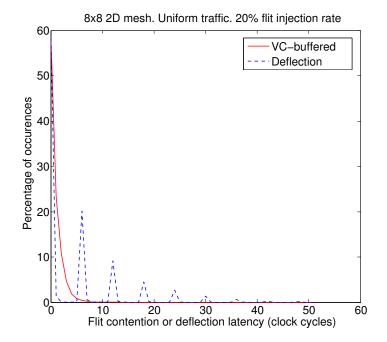

Figure 2.7: Blocking and deflection latency distribution.

Figure 2.7 shows the distribution of cycles that flits spend blocked in buffers or being deflected in the 2D mesh for a 20% injection rate. It was generated by subtracting the corresponding zero-load latency from each flit's measured latency. Since the latency imposed by an extra hop is 3 cycles (2 cycles to traverse a router and 1 to traverse a link), and each deflection adds an even number of hops, the deflection network histogram has spikes every 6 cycles. Thus, this graph also shows the distribution of the number of deflections per flit. In contrast, the VC network has a smooth latency distribution. The average blocking latency for the VC network is 0.75 cycles with a standard deviation of 1.18, while the maximum is 13 cycles. For the deflection network, the average is 4.87 cycles with a standard deviation of 8.09, while the maximum is 108 cycles. Since the average zero-load latency is 19.5 cycles, the VC network has 17% lower latency. These higher latency variations may be crucial to performance: in timeout-based protocols, high latencies will cause spurious retransmissions, and many workloads use synchronization primitives that are constrained by worst-case latency (e.g. barriers).

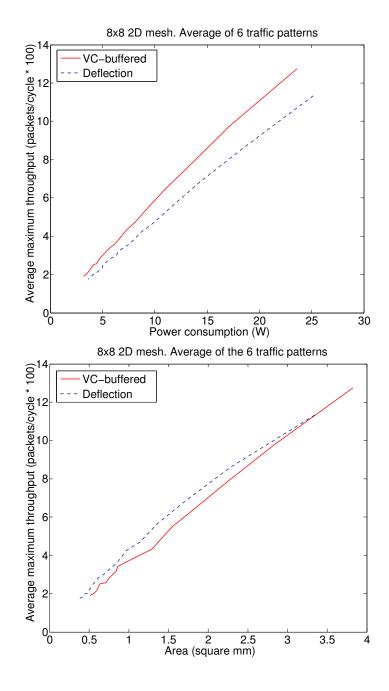

Figure 2.8 and Figure 2.9 show throughput versus area and power Pareto-optimal

Figure 2.8: Mesh throughput versus power and area Pareto-optimal curves.

Figure 2.9: FBFly throughput versus power and area Pareto-optimal curves.

Figure 2.10: Power and area breakdowns for the VC network in a 2D mesh under a 20% flit injection rate with full-swing channels.

Figure 2.11: Power assuming no empty buffer bypassing.

curves for both networks. Each point of each curve represents the maximum packet throughput achievable by a design of a given area or power. Results are averaged over the set of traffic patterns of each topology. These curves were generated by sweeping the datapath width so that a packet consists of 3 to 18 flits. They illustrate that power or area savings of a network can be traded for a wider datapath, which increases maximum throughput. Thus, points of equal area or power do not indicate an equal datapath width.

As illustrated, the mesh VC network provides 21% more throughput per unit power on average, and requires 19% less power to achieve equal throughput compared to BLESS. The deflection network provides 5% more throughput per unit area due to the buffers occupying 30% of the area, as explained in Section 2.4.2. Consequently, the deflection network requires 6% less area to achieve equal throughput. If the VC network was optimized for area, the buffers would be significantly smaller. The FBFly VC network provides 21% and 3% more throughput per unit power and area respectively. Achieving equal throughput requires 19% less power and 3% less area.

Widening the datapath favors the buffered network. While buffer and channel

costs scale linearly with datapath width, crossbar cost scales quadratically. Therefore, taking extra hops becomes more costly. Allocation cost becomes less significant because it is amortized over the datapath width. However, that cost is relatively small, as shown in Section 2.4.2. The quadratic crossbar cost is also the reason the VC FBFly is more area efficient than the deflection network, since widening the datapath to equalize throughput has a larger impact in the area of high-radix routers.

### 2.4.2 Power and Area Breakdown

Figure 2.10 shows the power and area breakdowns for the VC network in a 2D mesh with a 20% flit injection rate. Each router has 6 VCs, with 9 buffer slots per VC. The buffer cost without bypassing is included. Output clock and FF refer to the pipeline FFs at output ports that drive the long channel wires. Crossbar control is the power for the control wires routed to crossbar crosspoints. Channel traversal refers to the power to traverse the repeated channel segments. Channel clock is the clock wire power to the channel pipeline FFs. Leakage power is included for buffers and channels. For the FF buffers, the given power subsumes clocking, read and write power.

For a 20% flit injection rate, the average channel activity factor is 24.7% on the VC network and 29.3% on the deflection network. The extra 4.6% is due to deflections. This extra power equals  $5.5 \times$  the buffer access and leakage power. Buffer leakage power is only 0.6% of the overall network power. Removing the buffers saves 30% of the overall network area. The same SRAM buffers without bypassing consume  $8.5 \times$  the dynamic power with bypassing.

In general, there is no fixed relationship between the number of buffering events in a VC network and the number of deflections in a BLESS network, but intuitively, both increase at roughly the same rate with network utilization, as they depend on contention events. Thus, it is insightful to compare the energy of a buffer read and write with the energy consumed in a deflection. Writing and then reading a single 64-bit flit from and to an input buffer consumes 6.2pJ, while a channel and router traversal takes 20.9pJ (80% of this energy is consumed in the channel). A deflection induces at least 2 extra traversals, causing 42pJ of energy consumption,  $6.7 \times$  the dynamic energy for buffering the contending flit instead. Therefore, increasing router and channel traversals with deflections is not energy-efficient.

### 2.4.3 Low-swing Channels

Low-swing channels favor the deflection network because they reduce deflection energy and increase the ratio of the overall power made up by the buffers. With our lowswing channel model, the VC mesh network offers 16% more throughput per unit power than the deflection network for the mesh and 18% more for the FBFly. Also, the VC network offers comparable (1% more) throughput per unit area for the mesh, and 6% more for the FBFly. This increase in area efficiency for the VC network is due to differential signaling, which doubles the channel area, thus reducing the percentage of the total area occupied by the buffers to 19%. Moreover, the deflection network consumes less power for flit injection rates smaller than 11% for the mesh, and 8% for the FBFly. However, compared to the VC network, the power consumed by the deflection network is never less than 98.5% for the mesh and 99% for the FBFly. Figure 2.12 illustrates the results for the mesh. The networks are configured as in Section 2.4.1.

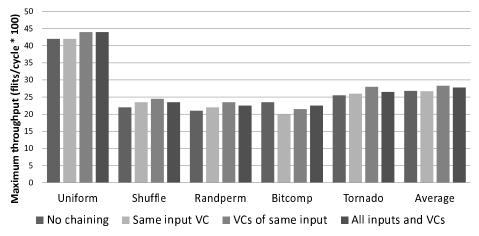

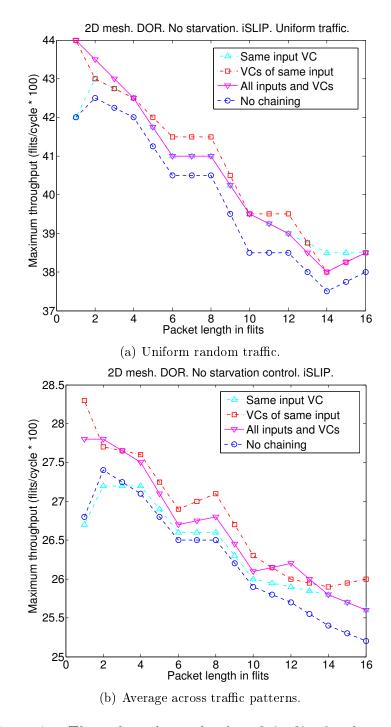

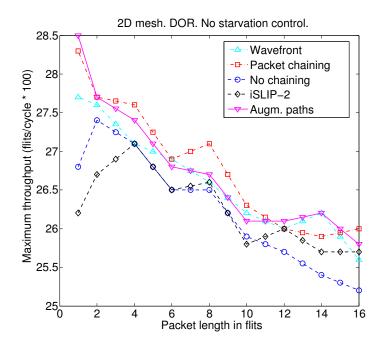

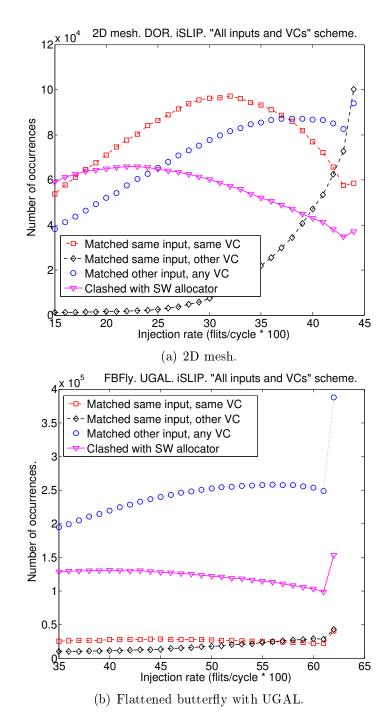

### 2.4.4 Deadlock and Endpoint Buffers