# **Roofline Performance Modeling for** HPC and Deep Learning Applications

**Charlene Yang**

NERSC

Lawrence Berkeley National Lab

CJYang@lbl.gov

## **Samuel Williams**

**Computational Research Division** Lawrence Berkeley National Lab SWWilliams@lbl.gov

## Schedule

Introduction to Roofline 9:00am 9:30am NVProf Methodology/demo **10:00am** Roofline Use Cases

Lawrence Berkeley National Lab yunsongwang@lbl.govv

BERKELEY NATIONAL LABORATORY

## Samuel Williams Yunsong Wang **Charlene Yang**

# Acknowled genents

- This material is based upon work supported by the Advanced Scientific Computing Research Program in the U.S. Department of Energy, Office of Science, under Award Number DE-AC02-05CH11231.

- This material is based upon work supported by the DOE RAPIDS SciDAC Institute.

- This research used resources of the National Energy Research Scientific Computing Center (NERSC), which is supported by the Office of Science of the U.S. Department of Energy under contract DE-AC02-05CH11231.

- This research used resources of the Oak Ridge Leadership Facility at the Oak Ridge National Laboratory which is supported by the Office of Science of the U.S. Department of Energy under Contract No. DE-AC05-000R22725.

# Introduction to the Roofine Model

## Samuel Williams

**Computational Research Division** Lawrence Berkeley National Lab SWWilliams@lbl.gov

# You just bought a \$10,000 throughput-optimized GPU!

# Are your making good use of your investment?

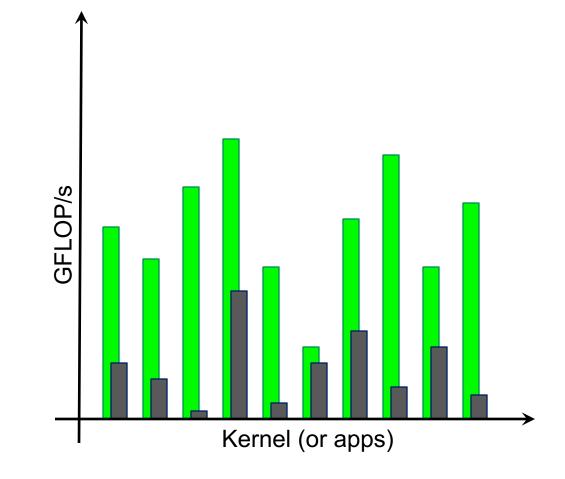

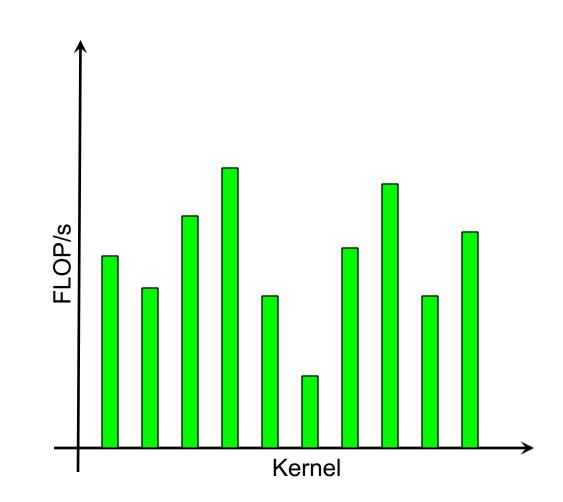

## You could just run benchmarks

- Imagine running a mix of benchmarks or kernels...

- GFLOP/s alone may not be particularly insightful

- speedup relative to a Xeon may seem random

- We need a quantitative model that defines <u>Good Performance</u>

- Good Performance is tied to "Efficient" execution

- Two fundamental requirements ...

- 1. Must operate the GPU in the throughput-limited regime not sensitive to Amdahl effects, D2H/H2D transfers, launch overheads, etc...

- 2. Must attain high utilization of the GPU's compute and/or bandwidth capabilities

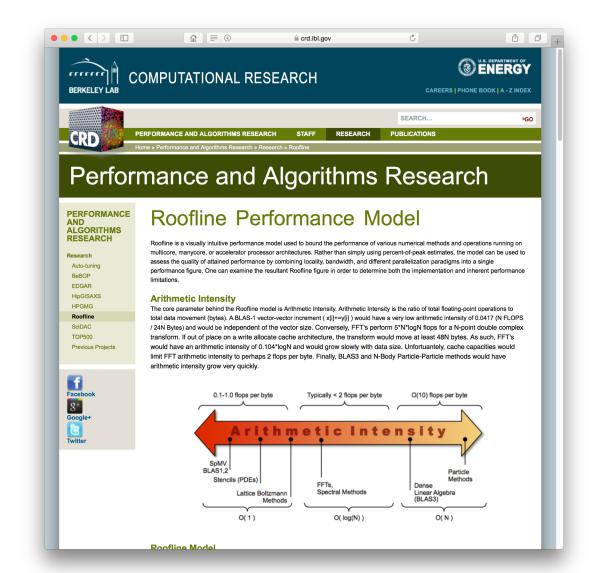

## **Roofline Model**

- **Roofline Model** is a throughput-oriented performance model

- applies to x86, ARM, POWER CPUs, GPUs, Google TPUs<sup>1</sup>, FPGAs, etc...

- Helps quantify **Good Performance**

https://crd.lbl.gov/departments/computer-science/PAR/research/roofline

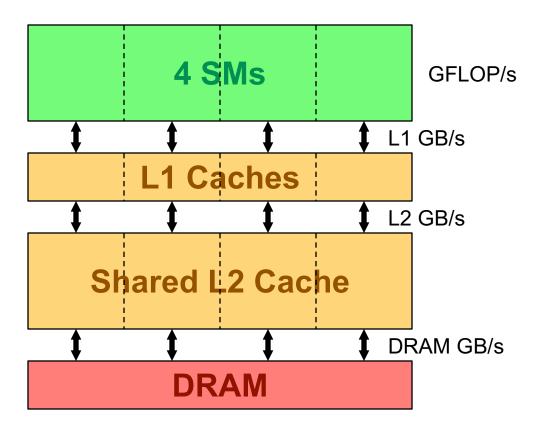

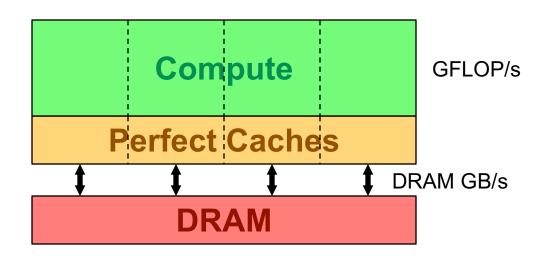

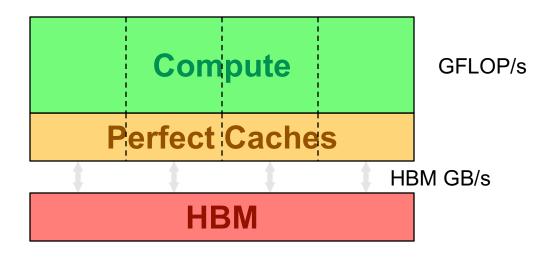

- GPU architectures can be complex

- Don't model / simulate full architecture

- Make assumptions on performance and usage...

- GPU architectures can be complex

- Don't model / simulate full architecture

- Make assumptions on performance and usage...

- Peak GFLOP/s on data in L1

- GPU architectures can be complex

- Don't model / simulate full architecture

- Make assumptions on performance and usage...

- $\circ$  Peak GFLOP/s on data in L1

- $\circ$  Load-balanced SPMD code

- GPU architectures can be complex

- Don't model / simulate full architecture

- Make assumptions on performance and usage...

- Peak GFLOP/s on data in L1

- Load-balanced SPMD code

- Sufficient cache bandwidth/capacity

- GPU architectures can be complex

- Don't model / simulate full architecture

- Make assumptions on performance and usage...

- Peak GFLOP/s on data in L1

- Load-balanced SPMD code

- Sufficient cache bandwidth/capacity

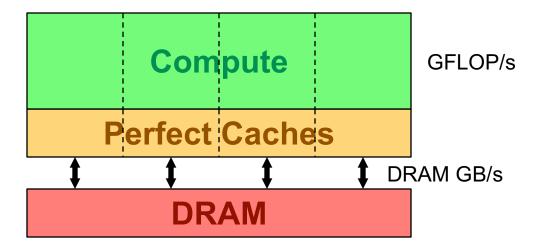

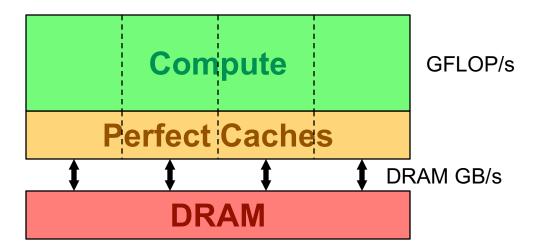

- Basis for DRAM Roofline Model

| Com        | p |

|------------|---|

| Perfect    | C |

| <b>† †</b> |   |

| DR         | A |

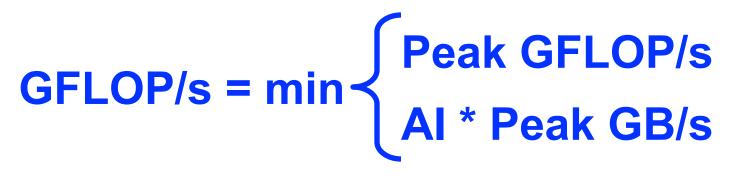

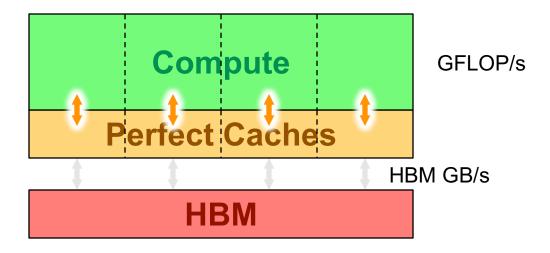

- Any given loop nest will perform:

- o Computation (e.g. FLOPs)

- Communication (e.g. moving data to/from DRAM)

- With perfect overlap of communication and computation...

$\circ$   $\,$  Run time is determined by whichever is greater  $\,$

Time = max { #FLOPs / Peak GFLOP/s #Bytes / Peak GB/s

- Any given loop nest will perform:

- o Computation (e.g. FLOPs)

- Communication (e.g. moving data to/from DRAM)

- With perfect overlap of communication and computation...

Time<br/>#FLOPs1 / Peak GFLOP/s#Bytes / #FLOPs / Peak GB/s

- Any given loop nest will perform:

- Computation (e.g. FLOPs)

- Communication (e.g. moving data to/from DRAM)

- With perfect overlap of communication and computation...

#FLOPs<br/>Time= min { Peak GFLOP/s<br/>(#FLOPs / #Bytes) \* Peak GB/s

- Any given loop nest will perform:

- Computation (e.g. FLOPs)

- Communication (e.g. moving data to/from DRAM)

- With perfect overlap of communication and computation...

- $\circ$   $\,$  Run time is determined by whichever is greater  $\,$

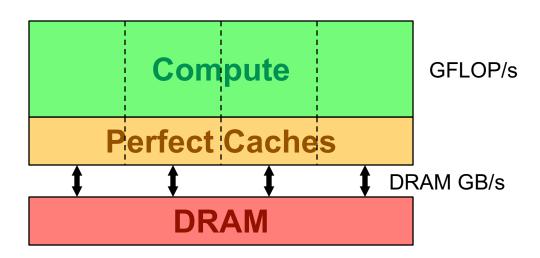

AI (Arithmetic Intensity) = FLOPs / Bytes (as presented to DRAM )

## **Arithmetic Intensity**

- Measure of data locality (data reuse)

- Ratio of <u>Total Flops</u> performed to <u>Total Bytes</u> moved

- For the DRAM Roofline...

- Total Bytes to/from DRAM

- $\circ$   $\,$  Includes all cache and prefetcher effects  $\,$

- Can be very different from total loads/stores (bytes requested)

- Equal to ratio of sustained GFLOP/s to sustained GB/s (time cancels)

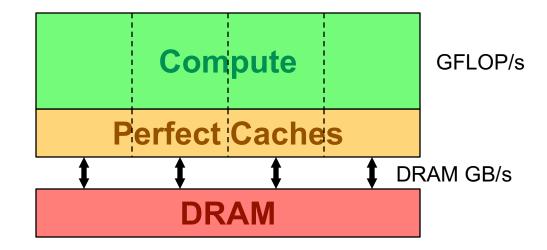

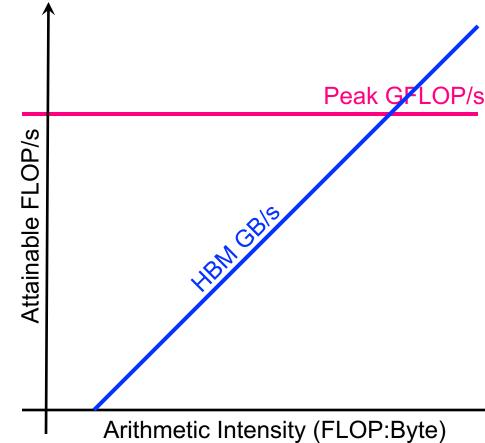

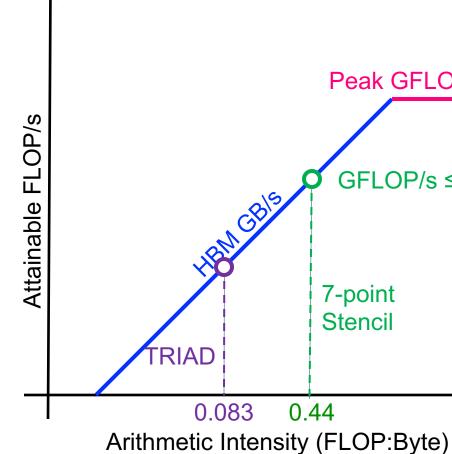

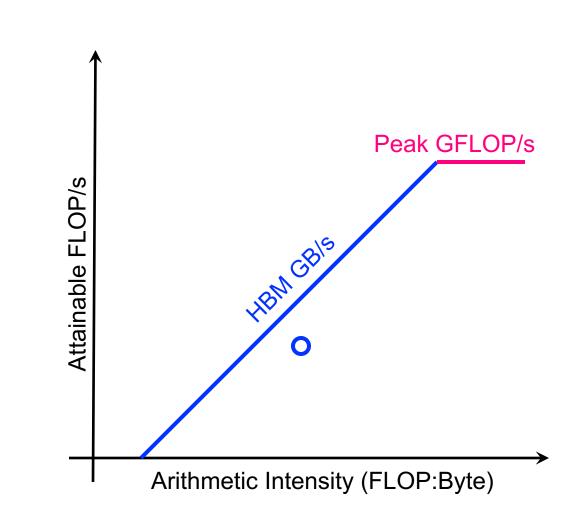

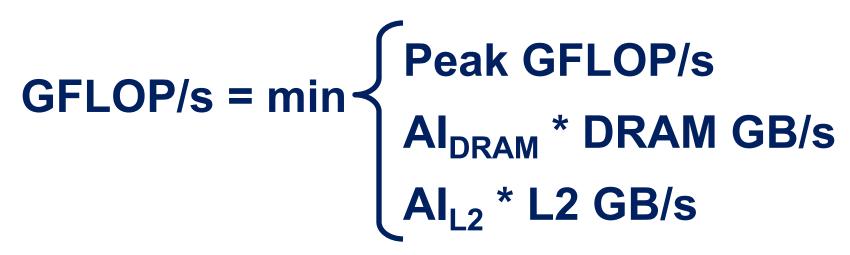

## (DRAM) Roofline Model

# GFLOP/s = min { AI \* Peak GB/s

AI (Arithmetic Intensity) = FLOPs / Bytes (moved to/from DRAM)

- Plot Roofline bound using Arithmetic Intensity as the x-axis

- Log-log scale makes it easy to doodle, extrapolate performance along Moore's Law, etc...

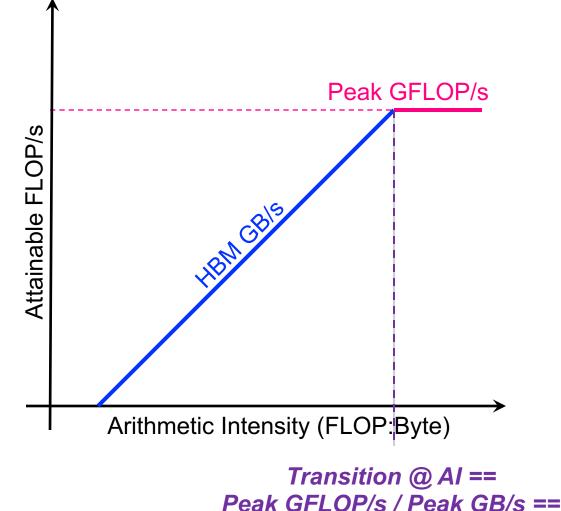

## (DRAM) Roofline Model

# GFLOP/s = min { AI \* Peak GB/s

AI (Arithmetic Intensity) = FLOPs / Bytes (moved to/from DRAM)

- Plot Roofline bound using Arithmetic Intensity as the x-axis

- Log-log scale makes it easy to doodle, extrapolate performance along Moore's Law, etc...

'Machine Balance'

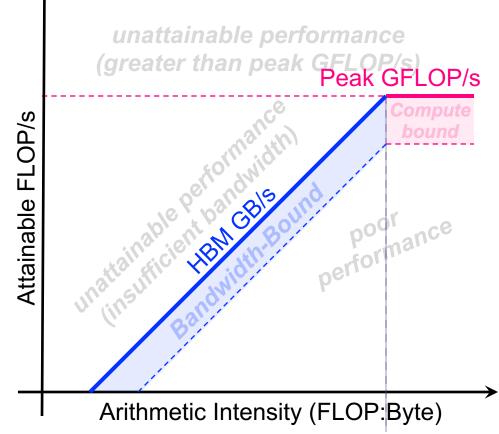

## (DRAM) Roofline Model

# Peak GFLOP/s AI \* Peak GB/s GFLOP/s = min

AI (Arithmetic Intensity) = FLOPs / Bytes (moved to/from DRAM)

Roofline tessellates this 2D view of performance into 5 regions...

Transition @ AI == Peak GFLOP/s / Peak GB/s == 'Machine Balance'

- Typical machine balance is 5-10

FLOPs per byte...

- $\circ$  40-80 FLOPs per double to exploit compute capability

- Artifact of technology and money

- o Unlikely to improve

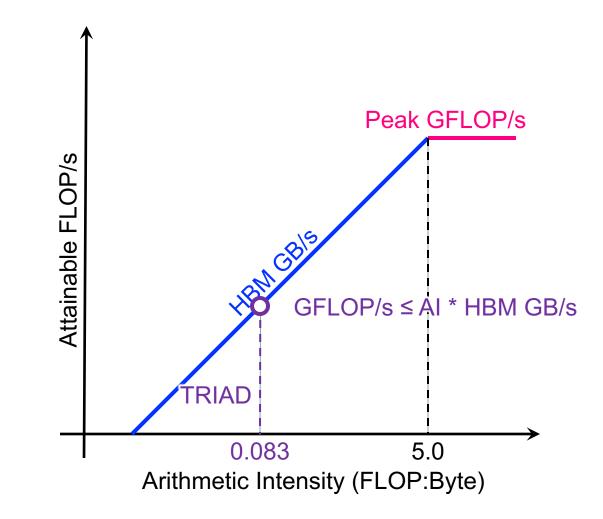

## Consider STREAM Triad...

#pragma omp parallel for for(i=0;i<N;i++){ Z[i] = X[i] + alpha\*Y[i]; }

- 2 FLOPs per iteration

- Transfer 24 bytes per iteration (read X[i], Y[i], write Z[i])

- AI = 0.083 FLOPs per byte == Memory bound

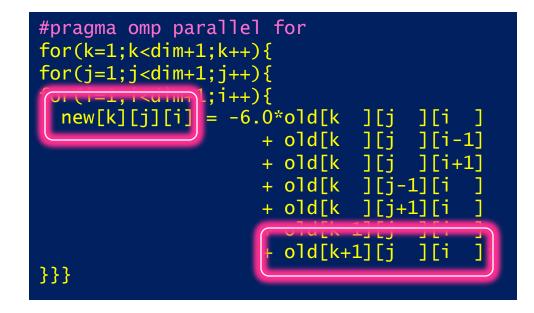

Conversely, 7-point constant coefficient stencil...

| <pre>#pragma omp parallel for for(k=1;k<dim+1;k++){ for(j="1;j&lt;dim+1;j++){&lt;/pre"></dim+1;k++){></pre> |

|-------------------------------------------------------------------------------------------------------------|

| <pre>for(i=1;i<dim+1;i++){< pre=""></dim+1;i++){<></pre>                                                    |

| new[k][j][i] = -6.0*old[k ][j ][i ]                                                                         |

| + old[k ][j ][i-1]                                                                                          |

| + old[k ][j ][i+1]                                                                                          |

| + old[k ][j-1][i ]                                                                                          |

| + old[k ][j+1][i ]                                                                                          |

| + old[k-1][j ][i ]                                                                                          |

| + old[k+1][j ][i ];                                                                                         |

| <pre>}}</pre>                                                                                               |

- Conversely, 7-point constant coefficient stencil...

- o 7 FLOPs

- o 8 memory references (7 reads, 1 store) per point

- AI = 7 / (8\*8) = 0.11 FLOPs per byte (measured at the L1)

- Conversely, 7-point constant coefficient stencil...

- o 7 FLOPs

- o 8 memory references (7 reads, 1 store) per point

- Ideally, cache will filter all but 1 read and 1 write per point

- Conversely, 7-point constant coefficient stencil...

- o 7 FLOPs

- o 8 memory references (7 reads, 1 store) per point

- o Ideally, cache will filter all but 1 read and 1 write per point

- 7 / (8+8) = 0.44 FLOPs per byte (DRAM)

```

#pragma omp parallel for

for(k=1;k<dim+1;k++){</pre>

for(j=1;j<dim+1;j++){</pre>

for(i=1;i<dim+1;i++){</pre>

new[k][j][i] = -6.0*old[k ][j

<u>+ old[k ][j ][i-1]</u>

+ old[k

][i ][i+1]

+ old[k

_][i-1][i

+ old[k ][i+1][i

+ old[k-1][i

1ſi

+ old[k+1][j _][i

1:

}}}

```

|   | Com    | р  |

|---|--------|----|

| P | erfect | C  |

| ţ | ţ      |    |

|   | HE     | 31 |

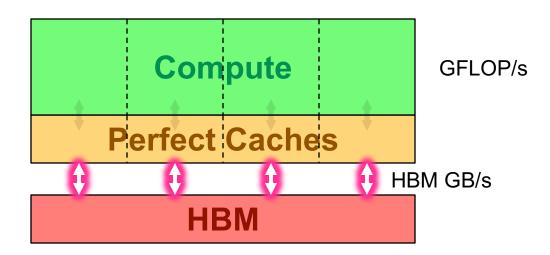

- Conversely, 7-point constant coefficient stencil...

- 7 FLOPs Ο

- 8 memory references (7 reads, 1 store) per point Ο

- Ideally, cache will filter all but 1 read and 1 write per point Ο

- 7 / (8+8) = 0.44 FLOPs per byte (DRAM)  $\succ$

== memory bound, but 5x the FLOP rate as TRIAD

| <pre>#pragma omp parallel for for(k=1;k<dim+1;k++){< pre=""></dim+1;k++){<></pre> |

|-----------------------------------------------------------------------------------|

| <pre>for(j=1;j<dim+1;j++){< pre=""></dim+1;j++){<></pre>                          |

| <pre>for(i=1;i<dim+1;i++){< pre=""></dim+1;i++){<></pre>                          |

| new[k][j][i] = -6.0*old[k ][j ][i ]                                               |

| + old[k ][j ][i-1]                                                                |

| + old[k ][j ][i+1]                                                                |

| + old[k ][j-1][i ]                                                                |

| + old[k ][j+1][i ]                                                                |

| + old[k-1][j ][i ]                                                                |

| + old[k+1][j ][i ];                                                               |

| }}}                                                                               |

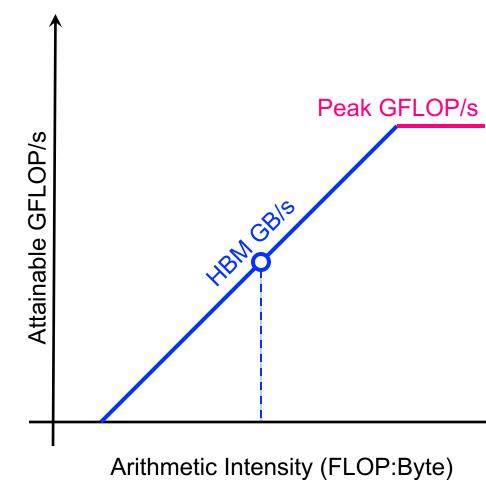

## Peak GFLOP/s GFLOP/s ≤ AI \* HBM GB/s

7-point Stencil

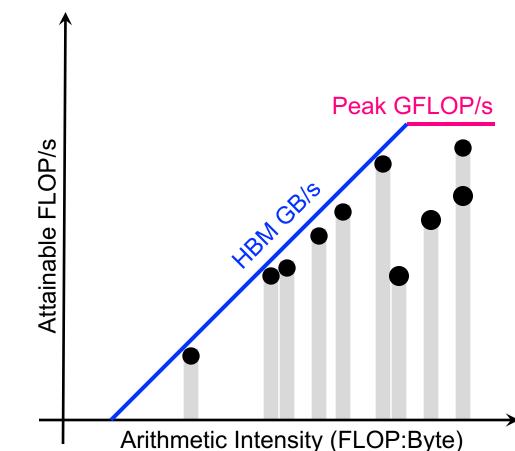

Think back to our mix of loop nests (benchmarks)...

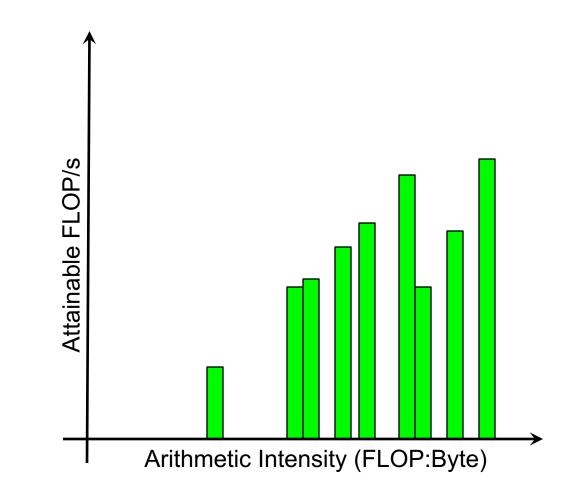

- Think back to our mix of benchmarks (kernels)

- We can sort kernels by their arithmetic intensity...

- Think back to our mix of benchmarks (kernels)

- We can sort kernels by their arithmetic intensity...

- ... and compare performance relative to machine capabilities

Kernels near the roofline are making good use of computational resources

- Kernels near the roofline are making good use of computational resources

- kernels can have low performance (GFLOP/s), but make good use (%STREAM) of a machine

- Kernels near the roofline are making good use of computational resources

- kernels can have low performance (GFLOP/s), but make good use (%STREAM) of a machine

- kernels can have high performance (GFLOP/s), but still make poor use of a machine (%peak)

# How can performance ever be below the Roofline?

## How can performance be below the Roofline?

- Does one always attain either...

- Peak DRAM Bandwidth  $\bigcirc$

- Peak FLOP/s

- Theoretical vs. Empirical

- Use benchmarked GFLOP/s and GB/s  $\bigcirc$

- Application FLOPs can be underestimated Ο (how many FLOPs is a divide?)

- Bottlenecks other than DRAM and FLOP/s...

- Insufficient cache bandwidth + locality Ο

- Didn't use FMA / Vectors / Tensors / ...  $\bigcirc$

- Too many non-FP instructions Ο

- etc...  $\bigcirc$

# Below the Roofine? Memory Hierarchy and Cache Bottlenecks

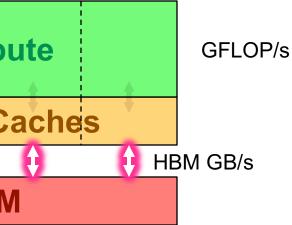

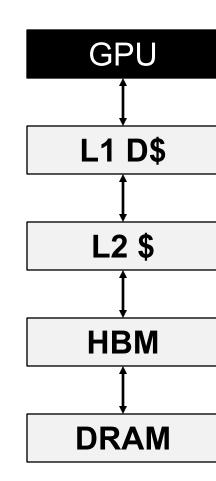

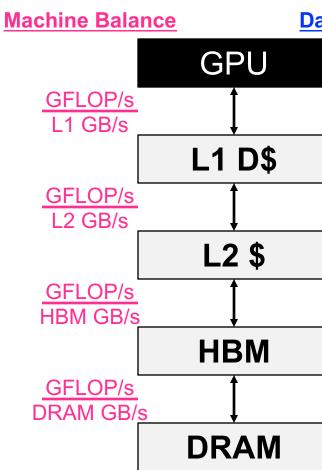

## **Memory Hierarchy**

- GPUs have multiple levels of memory/cache

- $\circ$  Registers

- $\circ$  L1, L2, cache

- HBM (GPU device memory)

- DDR (host memory)

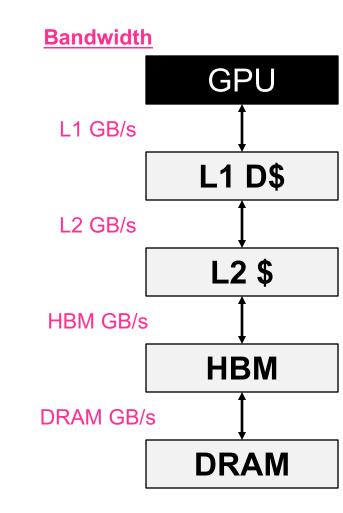

GPUs have different bandwidths for each level

- GPUs have different bandwidths for each level

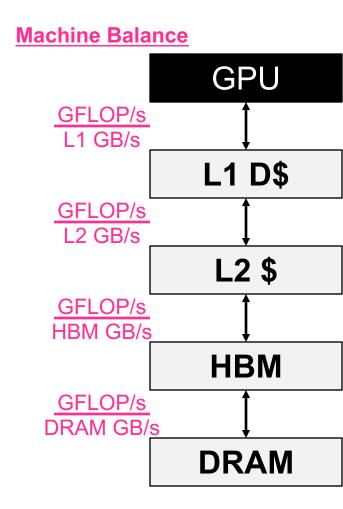

- o different machine balances for each level

- GPUs have different bandwidths for each level

- $\circ$  different machine balances for each level

- Applications have locality in each level

- o different data movements for each level

## Data Movement

## L1 GB

L2 GB

## HBM GB

DRAM GB

- GPUs have different bandwidths for each level

- $\circ$  different machine balances for each level

- Applications have locality in each level

- $\circ$  different data movements for each level

- o different arithmetic intensity for each level

## **Arithmetic Intensity**

GFLOPs L1 GB GFLOPs L2 GB GFLOPs HBM GB GFLOPs DRAM GB

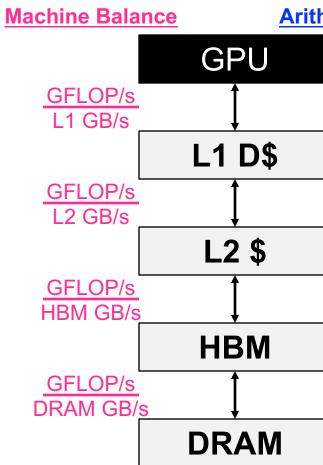

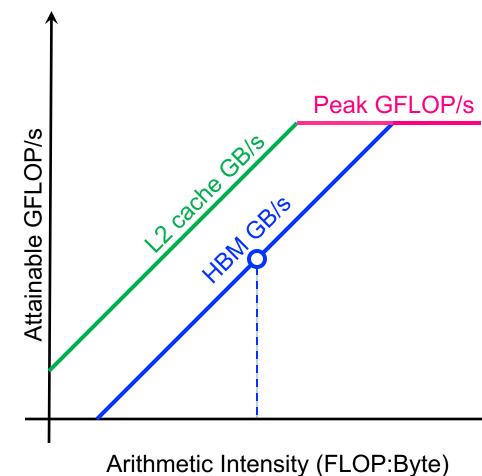

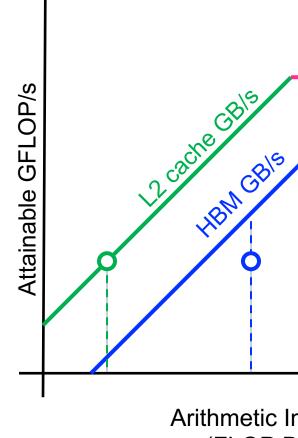

For each additional level of the memory hierarchy, we can add another term to our model...

$AI_x$  (Arithmetic Intensity at level "x") = FLOPs / Bytes (moved to/from level "x")

For each additional level of the memory hierarchy, we can add another term to our model...

$AI_x$  (Arithmetic Intensity at level "x") = FLOPs / Bytes (moved to/from level "x")

For each additional level of the memory hierarchy, we can add another term to our model...

Al<sub>x</sub> (Arithmetic Intensity at level "x") = FLOPs / Bytes (moved to/from level "x")

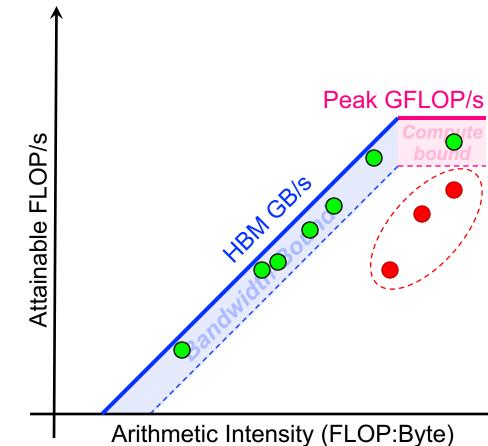

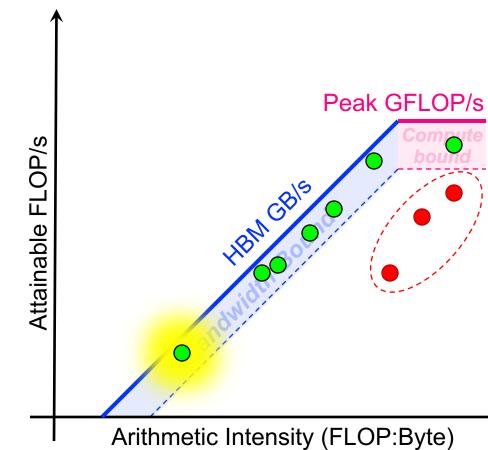

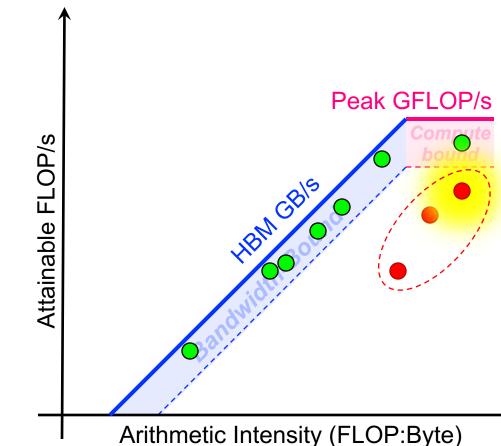

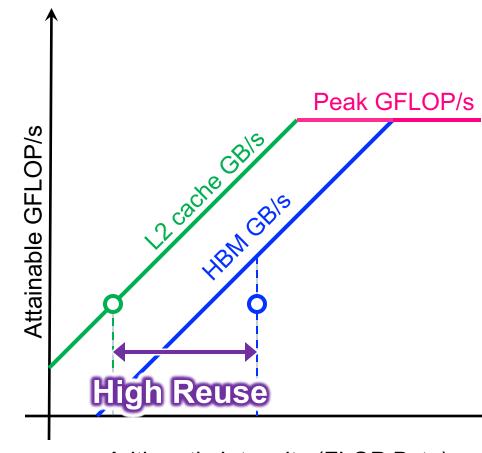

- Plot equation in a single figure...

- "Hierarchical Roofline" Model 0

- Plot equation in a single figure...

- "Hierarchical Roofline" Model Ο

- Bandwidth ceiling (diagonal line) for each Ο level of memory

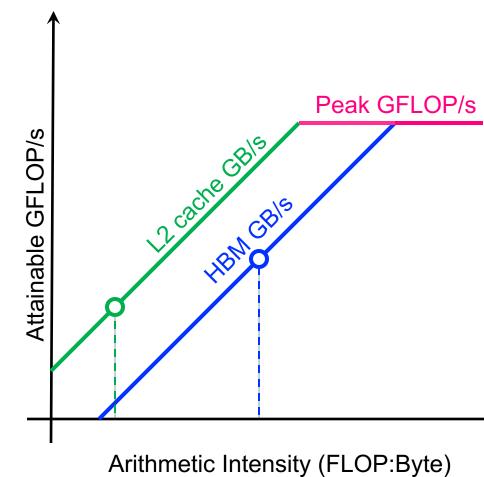

- Plot equation in a single figure...

- "Hierarchical Roofline" Model Ο

- Bandwidth ceiling (diagonal line) for each Ο level of memory

- Arithmetic Intensity (dot) for each level of Ο memory

- Plot equation in a single figure...

- "Hierarchical Roofline" Model  $\bigcirc$

- Bandwidth ceiling (diagonal line) for each Ο level of memory

- Arithmetic Intensity (dot) for each level of Ο memory

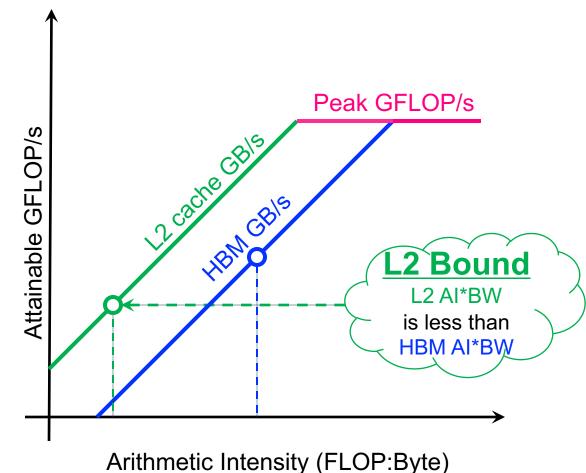

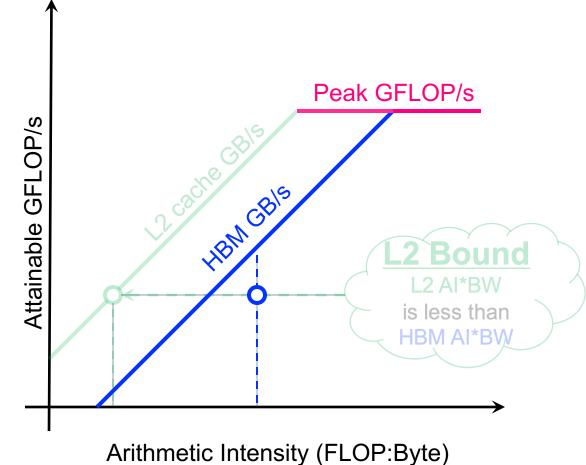

- performance is ultimately the minimum of these bounds

- Plot equation in a single figure...

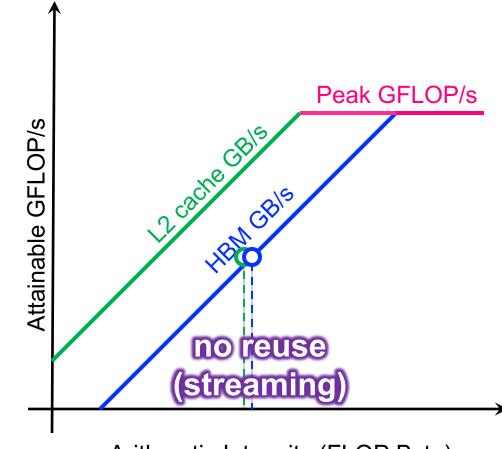

- "Hierarchical Roofline" Model  $\bigcirc$

- Bandwidth ceiling (diagonal line) for each Ο level of memory

- Arithmetic Intensity (dot) for each level of Ο memory

- performance is ultimately the minimum of these bounds

- If L2 bound, we see HBM dot well below HBM ceiling

Widely separated Arithmetic Intensities indicate high reuse in the cache

Arithmetic Intensity (FLOP:Byte)

- Widely separated Arithmetic Intensities indicate high reuse in the cache

- Similar Arithmetic Intensities indicate effectively no cache reuse (== streaming)

Arithmetic Intensity (FLOP:Byte)

# Below the Roofine? FMA, Reduced Precision, Tensor Cores

# **Return of CISC**

- Vectors have their limits (finite DLP, register file energy scales with VL, etc...)

- Death of Moore's Law is reinvigorating Complex Instruction Set Computing (CISC)

- Modern CPUs and GPUs are increasingly reliant on special (fused) instructions that perform multiple operations (fuse common instruction sequences)...

- FMA (Fused Multiply Add): z=a\*x+y ...*z*,*x*,*y* are vectors or scalars Ο

- 4FMA (Quad FMA): z=A\*x+z ... A is a FP32 matrix; x,z are vectors Ο

- WMMA (Tensor Core): Z=AB+C ...A, B are FP16 matrices; Z, C are FP32 Ο

- > If instructions are a mix or scalar (predicated), vector, and matrix operations, performance is now a weighted average of them.

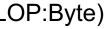

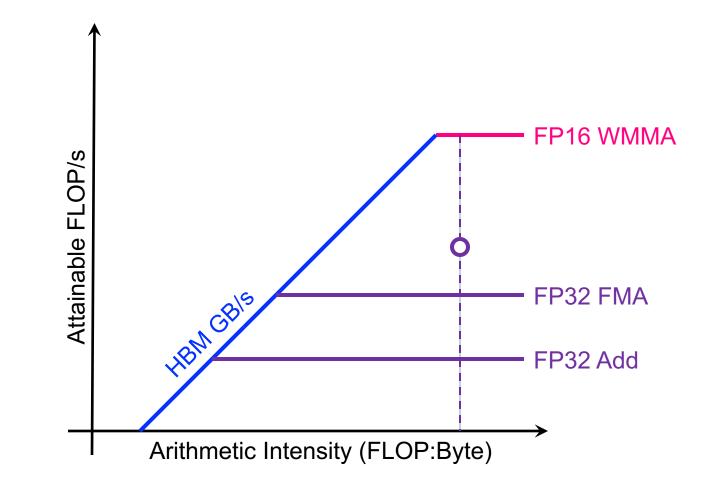

# **Return of CISC**

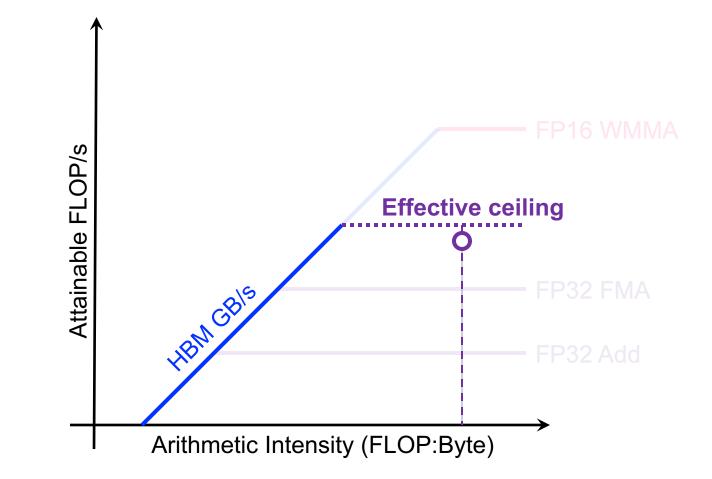

- Consider NVIDIA Volta GPU...

~100 TFLOPs for FP16 Tensor

15 TFLOPS for FP32 FMA

7.5 TFLOPs for FP32 Add

- DL applications mix Tensor, FP16, and FP32

- DL performance may be well below nominal Tensor Core peak

# **Return of CISC**

- Consider NVIDIA Volta GPU…

- ~100 TFLOPs for FP16 Tensor

- $\circ$   $\,$  15 TFLOPS for FP32 FMA  $\,$

- $\circ$   $\,$  7.5 TFLOPs for FP32 Add  $\,$

- DL applications mix Tensor, FP16, and FP32

- DL performance may be well below nominal Tensor Core peak

- The actual mix of instructions introduces an <u>effective ceiling</u> on performance...

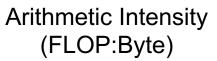

# Below the Roofine? FPU Starvation and Instruction Roofline

## Think about classifying apps by instruction mix...

- Heavy floating-point (traditional FLOP Roofline)

- Mix of integer and floating-point (FPU starvation) Integer-only (e.g. bioinformatics, graphs, etc...)

- Mixed precision (e.g. deep learning)

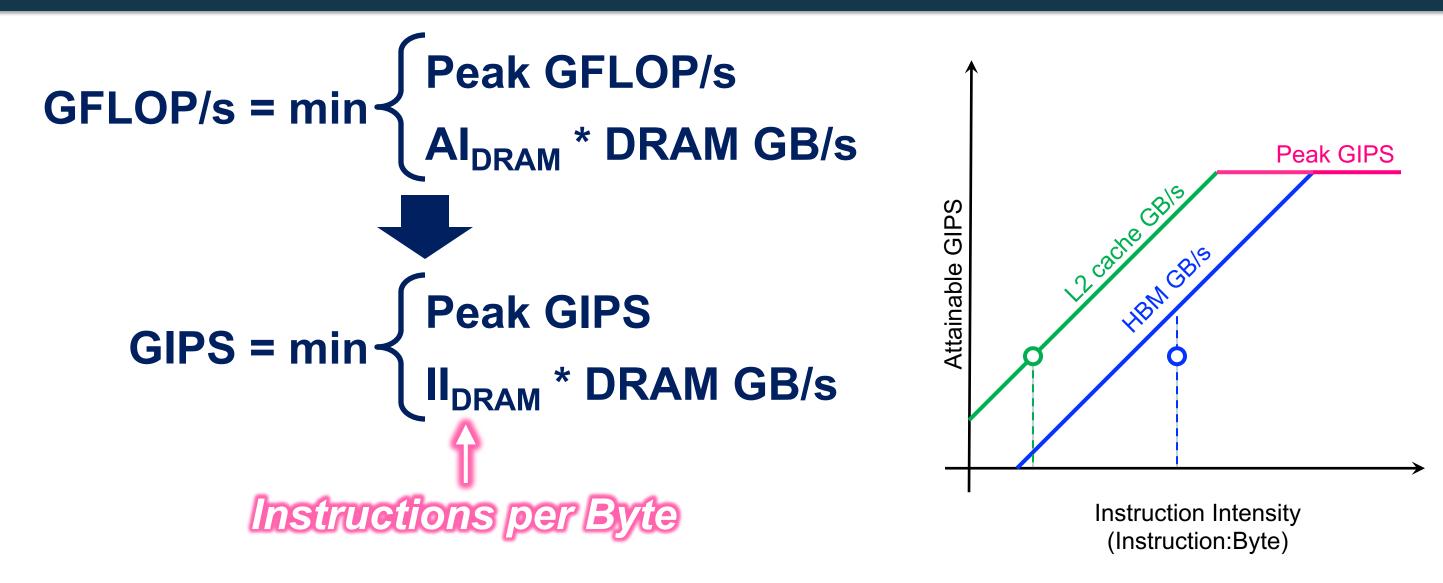

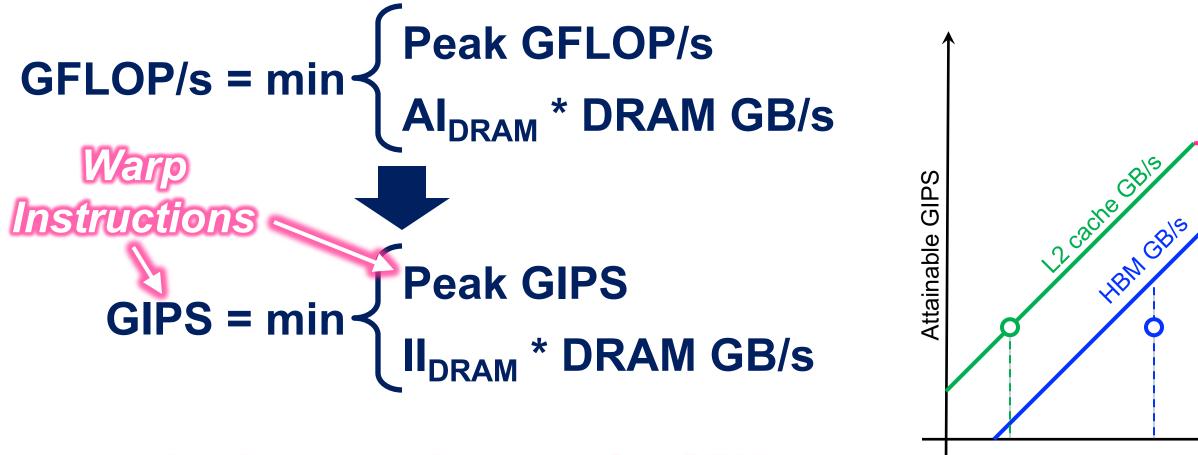

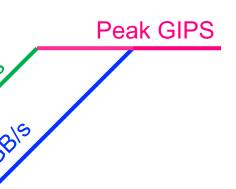

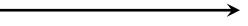

# **NVIDIA GPU Instruction Roofline**

- Instructions per second? Instructions per Byte?

- What is an 'Instruction' on a GPU?

- Thread-level hides issue limits?  $\bigcirc$

- Warp-level hides predication effects? Ο

- Scale non-predicated threads down by the warp size (divide by 32) Ο

- Naively, one would think instruction intensity should use 'bytes'

- GPUs access memory using 'transactions'

- 32B for global/local/L2/HBM

- 128B for shared memory Ο

- "Instructions/Transaction" preserves traditional Roofline, but enables a new way of understanding memory access

## **Instruction Roofline**

64

## **Instruction Roofline**

## Instruction Roofline on GPUs

As the natural quanta for GPU memory access is a "transaction"....

Instruction Intensity

## Instruction Roofline on GPUs

Instruction Intensity (Instruction:Transaction)

Instructions / Transactions (to/from level "x")

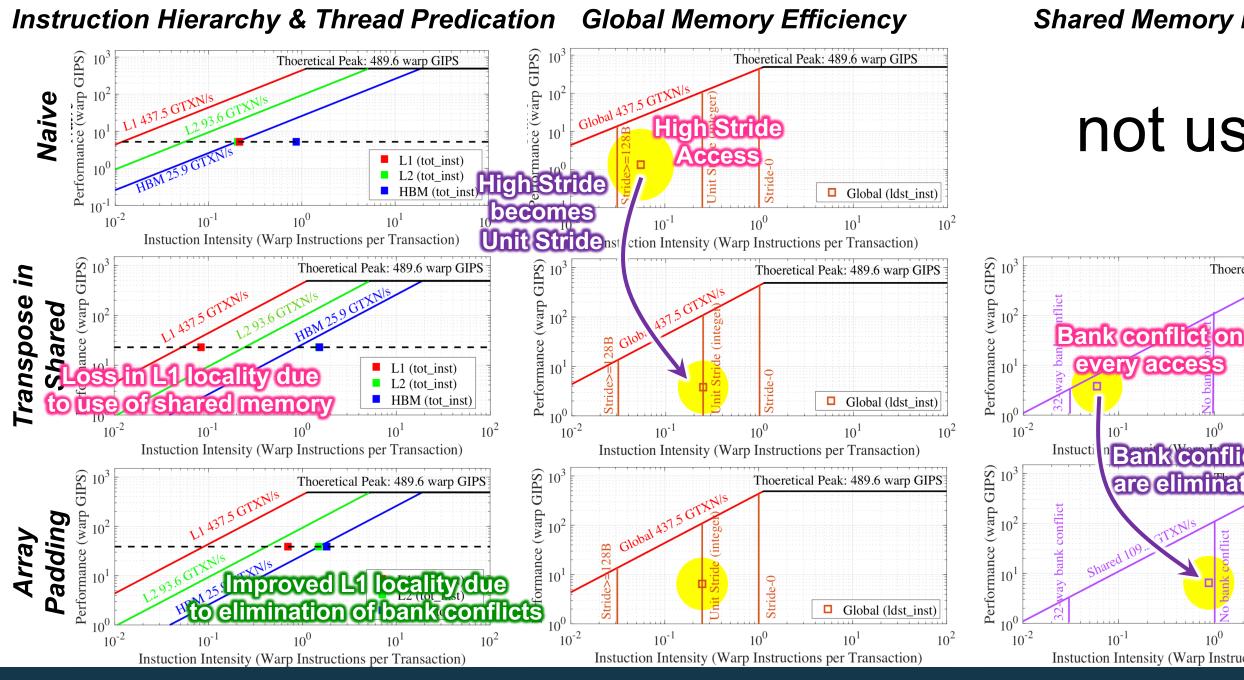

# Efficiency of Global Memory Access

- (Global)LDST Instruction Intensity has a special meaning / use...

- **Global LDST instructions / Global transactions**  $\bigcirc$

- Numerator lower than nominal II  $\bigcirc$

- Denominator can be lower than nominal L1 II (no local or shared transactions) Ο

- Denotes efficiency of memory access

- 3 "Walls" of interest:

- ≥1 transaction per LDST instruction Ο (all threads access same location)

- ≤32 transactions per LDST instruction Ο (gather/scatter or stride>=128B)

- Unit Stride: 1 LDST per 8 transactions Ο (double precision)

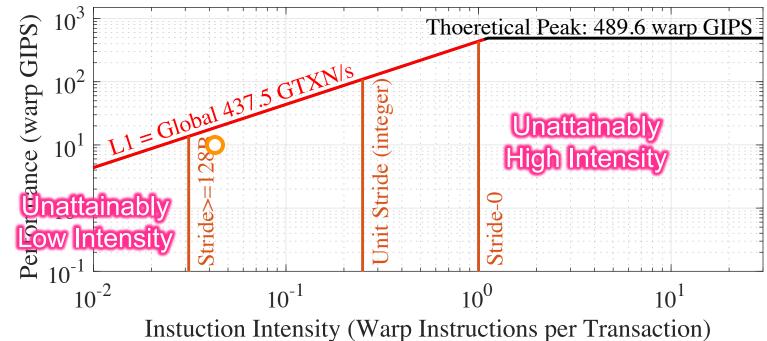

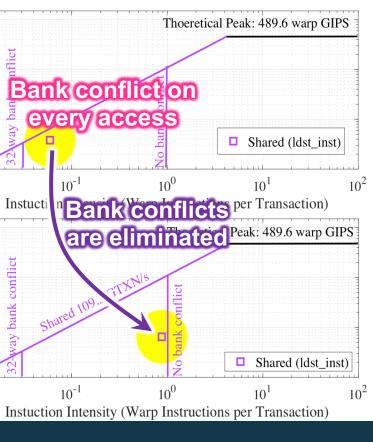

# Efficiency of Shared Memory Access

- (Shared)LDST Instruction Intensity also has a special meaning / use

- Shared LDST instructions / Shared transactions  $\bigcirc$

- It is similarly loosely related to nominal II Ο

- Can be used to infer the number of bank conflicts

- 2 "Walls" of interest:

- Minimum of 1 transaction per shared Ο LDST instruction (*no bank conflicts*)

- Maximum of 32 transactions per Ο shared LDST instruction (all threads access different lines in the same bank)

BERKELEY

# Instruction Roofline for Matrix Transpose

Nan Ding, Samuel Williams, "An Instruction Roofline Model for GPUs". PMBS. November. 2019.

70

## Shared Memory Efficiency

## not used

BERKELEY LAB LAWRENCE BERKELEY NATIONAL LABORATORY

# **Roofline Recap**

## **Bounds performance**

- Horizontal Lines = Compute Ceilings

- Diagonal Lines = Bandwidth Ceilings

- Bandwidth ceilings are parallel on log-log scale

- > Collectively, ceilings define an upper limit on performance

## Arithmetic Intensity

- Different intensity for each level of memory

- Total FLOPs / Total Data Movement

- Includes <u>all</u> cache effects

- > Measure of a loop's temporal locality

## **Plotting loops...**

- level of memory

- x-coordinate =

- y-coordinate = **GFLOP**/s

- cache locality

Each loop has one dot per Al at that level

Proximity to associated ceiling is indicative of a performance bound

> Position of dots relative to each other is indicative of

# Instruction Roofline Takeaway

## **Traditional Roofline**

- Tells us about performance (floating-point)

- Intensity based on data locality (FLOPs / Bytes)

- Use of FMA, SIMD, vectors, tensors has no affect on intensity

- Presence of integer instructions has no affect on intensity.

- Reducing precision (64b, 32b, 16b) increases arithmetic intensity

## **Instruction Roofline**

- Tells us about bottlenecks *(issue and memory)*

- Intensity based on total instructions and transactions

- Use of FMA, SIMD, vectors, tensors decreases intensity.

- Presence of integer instructions increases intensity.

- Reducing precision has no affect on intensity

## **Memory Walls**

- (memory access)

- Intensity based on LDST instructions and transactions

**Tells us about efficiency**

Reducing precision shifts intensity and the unit-stride wall

# What is Roofline used for?

- Understand performance differences between Architectures, Programming Models, implementations, etc...

- Why do some Architectures/Implementations move more data than others? Ο

- Why do some compilers outperform others? Ο

- Predict performance on future machines / architectures

- Set realistic performance expectations 0

- Drive for HW/SW Co-Design Ο

- Identify performance bottlenecks & motivate software optimizations

- Determine when we're done optimizing code

- Assess performance relative to machine capabilities Ο

- Track progress towards optimality Ο

- Motivate need for algorithmic changes Ο