NATIONAL LABORATORY

## Parallelism and Performance

### **Samuel Williams**

Computational Research Division Lawrence Berkeley National Lab

LAWRENCE BERKELEY NATIONAL LABORATORY

## Acknowledgements

- This material is based upon work supported by the Advanced Scientific Computing Research Program in the U.S. Department of Energy, Office of Science, under Award Number DE-AC02-05CH11231.

- This material is based upon work supported by the DOE RAPIDS SciDAC Institute.

- This research used resources of the National Energy Research Scientific Computing Center (NERSC), which is supported by the Office of Science of the U.S. Department of Energy under contract DE-AC02-05CH11231.

- This research used resources of the Oak Ridge Leadership Facility at the Oak Ridge National Laboratory, which is supported by the Office of Science of the U.S. Department of Energy under Contract No. DE-AC05-00OR22725.

LAWRENCE BERKELEY NATIONAL LABORATORY

## Parallelization

### **Multicore Node Architectures**

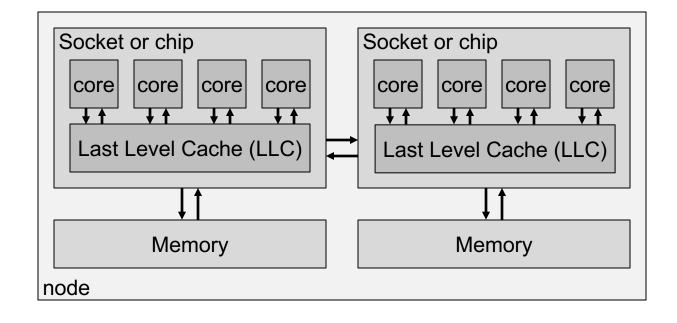

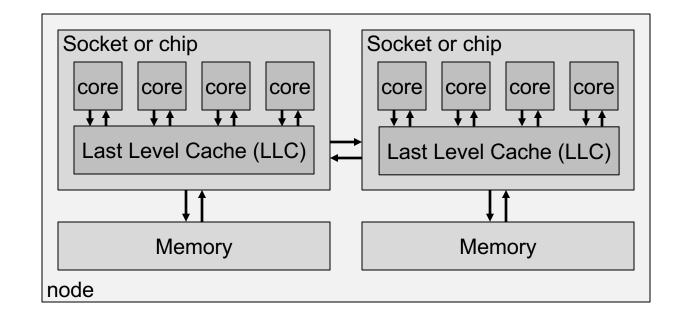

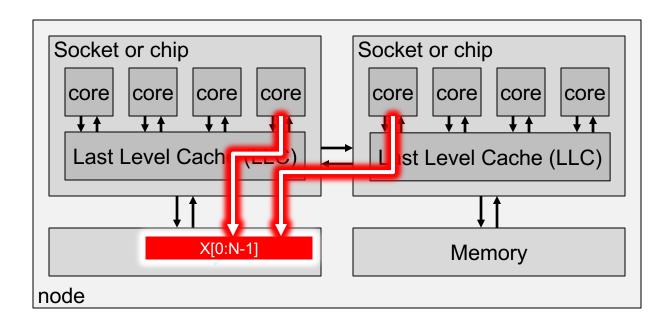

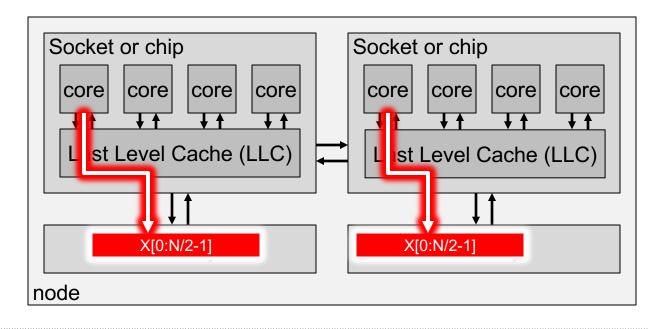

- Imagine a dual-socket, guad-core node...

- Each socket has a shared last level cache  $\bigcirc$ and its own directly attached memory

- Between sockets, there is an interconnect Ο (e.g. QPI, HT, etc...) that allows one socket to read another's memory/caches

### **GPU-Accelerated Nodes**

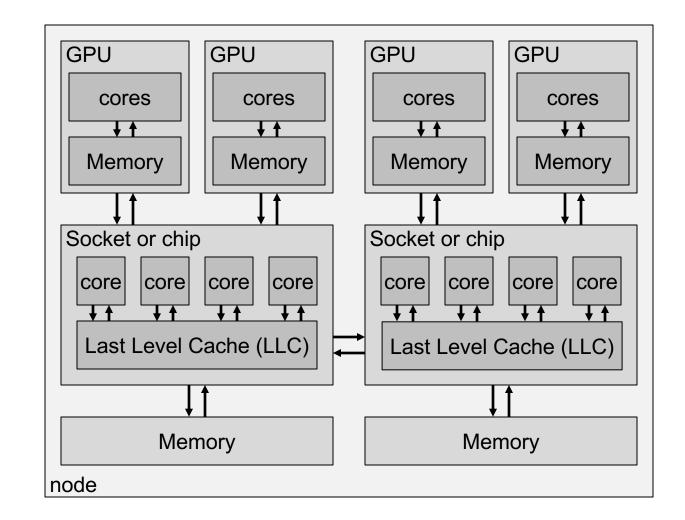

- Imagine a dual-socket, quad-core node...

- Each socket has a shared last level cache and its own directly attached memory

- Between sockets, there is an interconnect (e.g. QPI, HT, etc...) that allows one socket to read another's memory/caches

- Additionally, we may attach multiple GPUs per socket...

- Each GPU has its own cores, caches, and memory.

- Depending on the GPU, it can directly read host memory or other GPUs memory via loads/stores

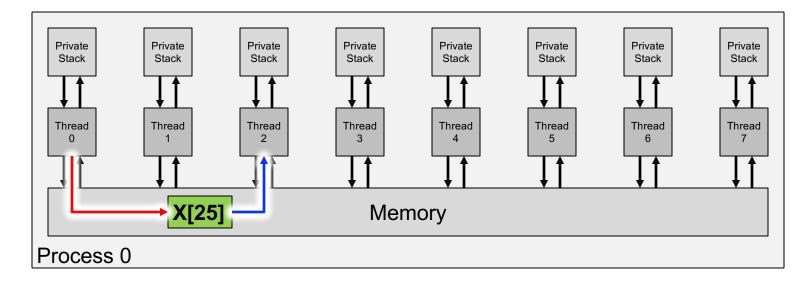

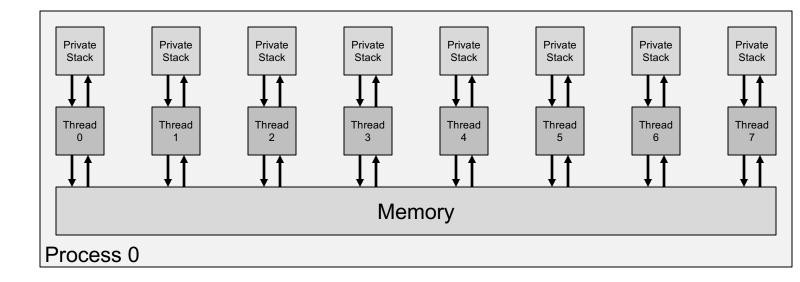

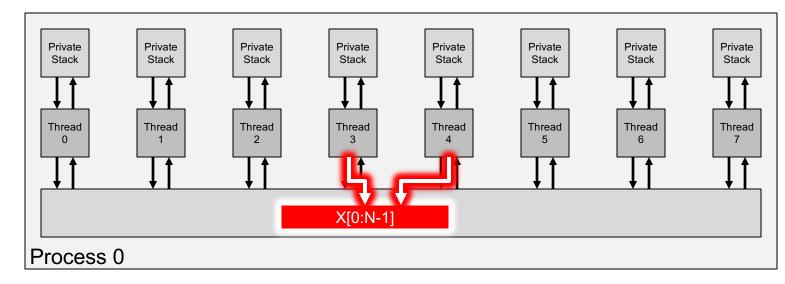

We can apply a shared memory programming model (OpenMP/pthreads) and abstract away hardware...

- We can apply a shared memory programming model (OpenMP/pthreads) and abstract away hardware...

- As such, from SW POV, all we might see is threads and memory (no caches, sockets, cores)

- Threads read/write memory locations to exchange data

| <u>Thread0</u><br>X[25] = 3.14; | Thread 2                 |

|---------------------------------|--------------------------|

|                                 | <br>temp = X[25] * Y[27] |

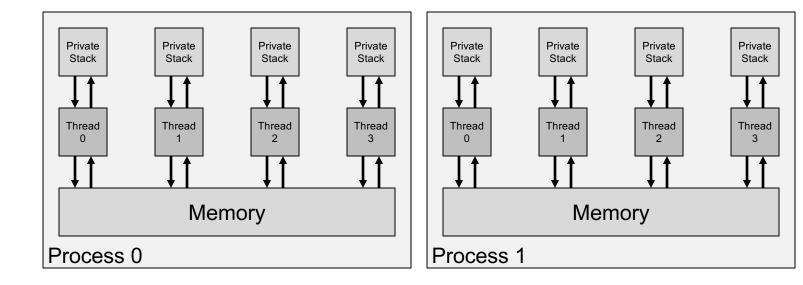

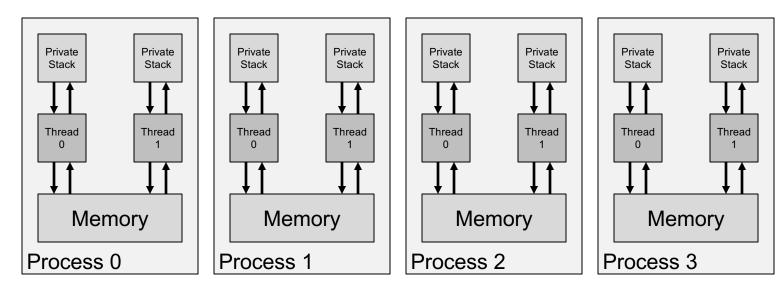

Rather than only using threads, we can combine programming models (Hybrid)

- Rather than only using threads, we can combine programming models (Hybrid)

- For example, we can combine MPI w/OpenMP…

- 2 processes per node

- $\circ$  4 threads per process

- With proper control of affinity (srun and omp), we can efficiently map this to hardware.

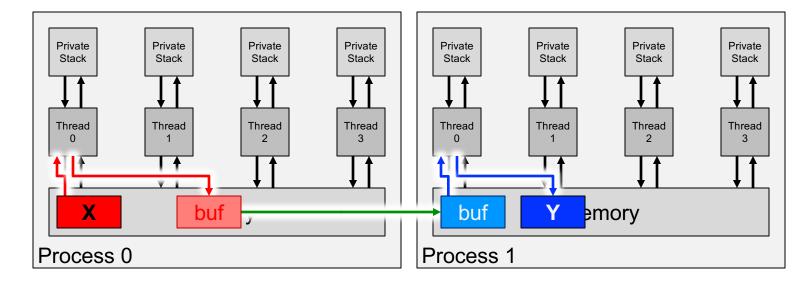

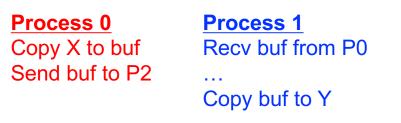

- Each process has its own private memory that cannot be read by the other process

- Communication among threads within a process is handled via shared memory

- Processes send/receive messages to exchange data

- Messages are tagged by rank, ID, and communicator

- Recv's on the destination can be posted before a Send has been posted on the host (blocks)

- Asynchronous communication (isend/irecv) is non-blocking but requires a wait to ensure completion.

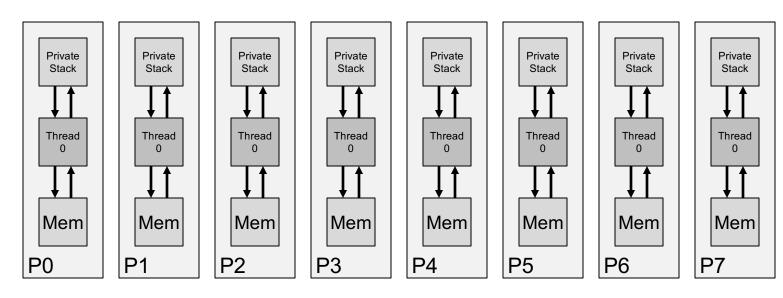

- We can select and combination of processes and threads on a node...

- Its best not to oversubscribe hardware (procs \* threads == cores)

- Always use affinity to bind processes and threads cognizant of the underlying hardware.

- We can select and combination of processes and threads on a node...

- Its best not to oversubscribe hardware (procs \* threads == cores)

- Always use affinity to bind processes and threads cognizant of the underlying hardware.

- Note, OMP\_NUM\_THREADS==1 is not the same as flat MPI (no –qopenmp)

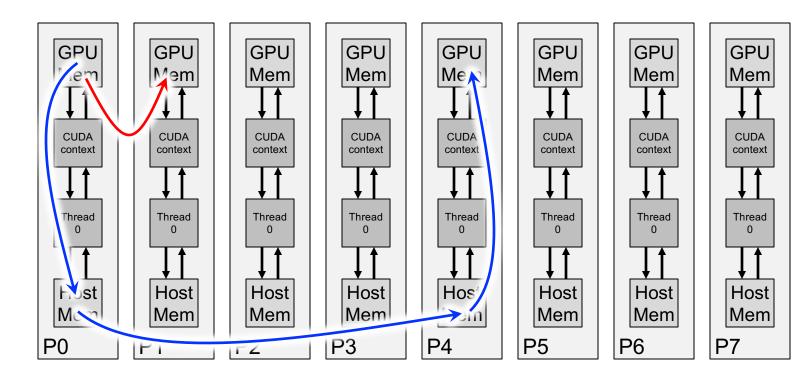

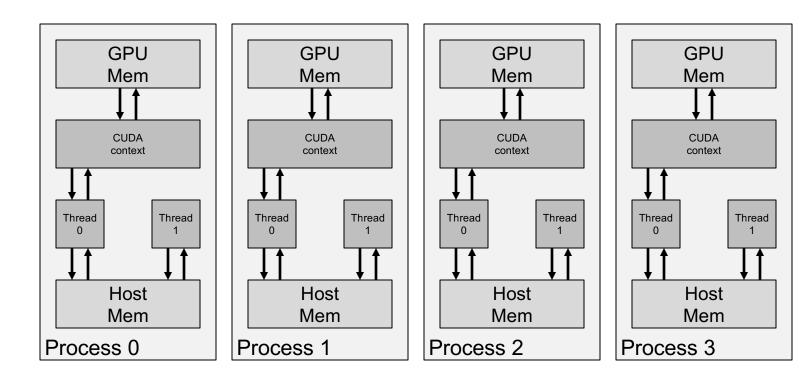

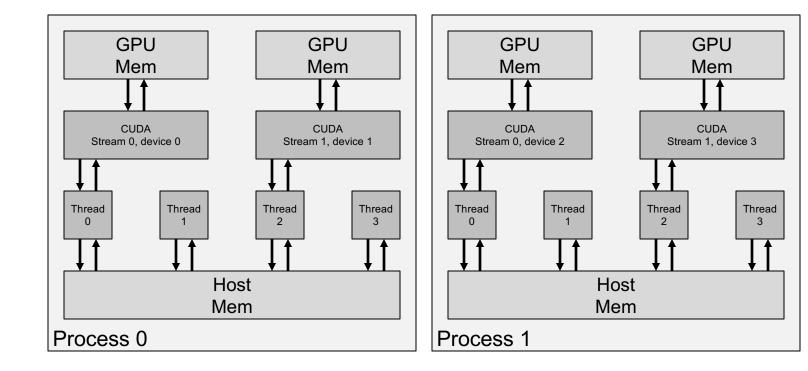

- Newer GPUs allow multiple processes to share a single GPU

- o each gets a 'context'

- GPU memory is portioned among contexts

- Processes either time multiplex(older) resources or run concurrently

- Efficiency of GPU-GPU MPI exchanges is implementation dependent

- One process per CPU core may not efficiently utilize a GPUaccelerated system

- As such, one could run one process per GPU...

- As such, one process per CPU core may not efficiently utilize a GPU-accelerated system

- As such, one could run one process per GPU...

- In or one process per socket.

- Unfortunately, having one process control multiple GPUs can be harder to program (multiple streams)

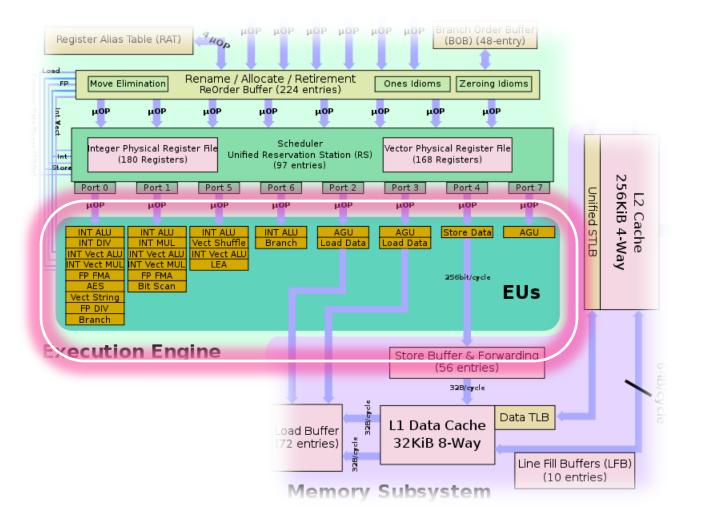

### **Intra-Core Parallelization**

- Within each core there can be parallelism...

- Multiple functional units (ILP)

- Vectors/SIMD (DLP)

- Specialized functional units (FMA, Tensor Cores, etc...)

- Pipeline parallelism (ILP)

- Discovery can be done at compile time (vectors) or run time (ILP)

- Failure to exploit these limits performance

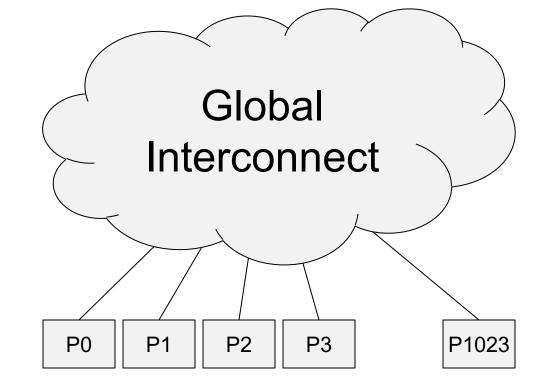

### Multi-Node (Distributed Memory) Parallelization

- MPI is used for multi-node parallelization

- From the user standpoint, on-node and inter-node MPI Ο looks the same

- All communication is handled via MPI (P2P or Ο collectives)... no shared memory communication

- UPC, CAF, GA provide shared memory abstraction.

- Memory balancing...

- can't shift memory capacity from one node to another. Ο

- If any one node exceeds its memory capacity, the job Ο will crash w/OOM error

- Swap is rare (diskless compute nodes) Ο

### **Synchronization**

- When one thread (or process) produces data and another thread (or process) consumes it, we have a data hazard

- We must synchronize to resolve the data hazard and ensure determinism & correctness.

## **Synchronization**

- In the P2P MPI world, synchronization is automatic in the irecv/isend/waitall/compute paradigm

- In the OpenMP world, we must explicitly synchronize...

- Easiest solution: leverage BSP model...

- #pragma omp parallel implies an implicit Ο barrier

- Data is only exchanged between parallel Ο regions (never within)

- **Coarse grained** Ο

- Finer grained...

- Use OMP reductions, atomics, locks, and Ο critical sections

LAWRENCE BERKELEY NATIONAL LABORATORY

## Challenges

### **Load Balancing**

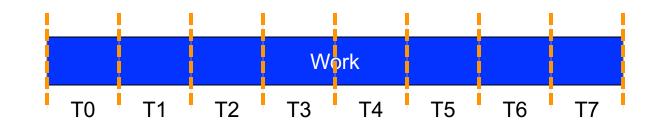

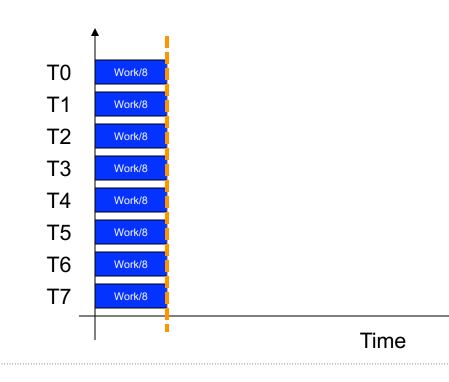

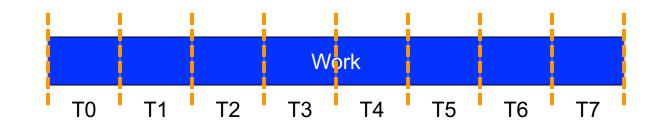

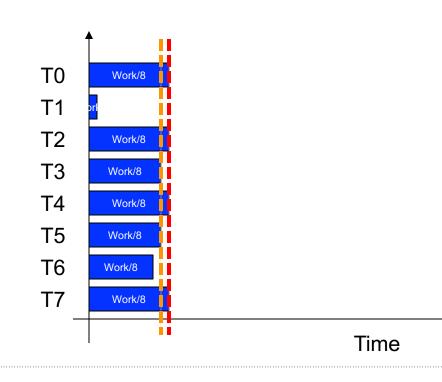

Imagine we have some work to partition (e.g. computation on an array)

Ο

- ray) We can try and uniformly partition work (loop iterations) among threads

- Ideally, the run time should be reduced by 1/NThreads

### **Load Balancing**

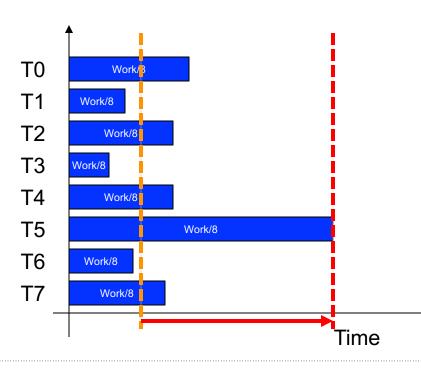

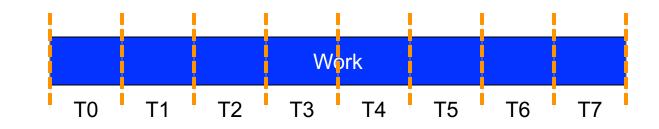

- Unfortunately, some loop iterations may be more expensive, or some threads may run slower (e.g. cache effects)

- As a result, we can observe load imbalance where run time is limited by the slowest thread

- We can assess the degree of load imbalance by measuring max/average

- A slow outlier may substantially hurt performance, but...

### **Load Balancing**

- Unfortunately, some loop iterations may be more expensive, or some threads may run slower (e.g. cache effects)

- As a result, we can observe load imbalance where run time is limited by the slowest thread

- We can assess the degree of load imbalance by measuring max/average...

- A slow outlier may substantially hurt performance, but...

- $\circ$  ...a fast thread may not help or hurt much

### Lack of Parallelism

- Trends in architecture have enabled >>1000-way parallelism on a chip (#FPUs \* FPU latency)

- Not all loop nests support 1000-way parallelization

- Loop nests with <1000-way parallelism underutilize HW resources

- Often codes must be restructured to enable more parallelism

- Loops are reordered/fused (OMP collapse(3)) Ο

- Variables(arrays) are privatized and reduced Ο

- Nominally sequential functions/solvers on independent variables are performed Ο concurrently (MPI sub communicators or OMP Tasks)

- Workflows/multiphysics are parallelized at launch (SLURM MPMD) Ο

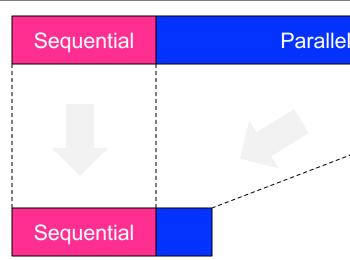

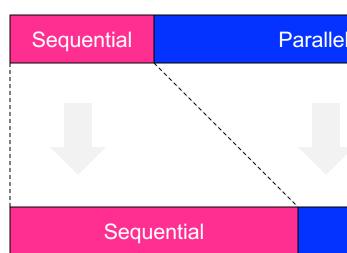

### Amdahl's Law & Bottlenecks

In an application, not every loop might be parallelized.

- Speedup =  $(f_{seg} + f_{par}/S_{par})^{-1}$

- 8x speedup on 75% of the run time Ο provides a 3x speedup

- Infinite speedup on 75% of the run time 0 only provides a 4x speedup.

- Similar effect applies to vectors, GPUs, and other accelerators.

- o e.g. GPU providing 10x on 10% of an application = 10% speedup.

Time

# Parallelizable loops

### Amdahl's Law & Bottlenecks

Time

- On manycore processors (KNL), single thread performance is worse than Haswell

- Parallel parts of apps get faster Ο

- Sequential parts get slower Ο

- **Overall benefit is less than expected** Ο

### Parallelizable loops

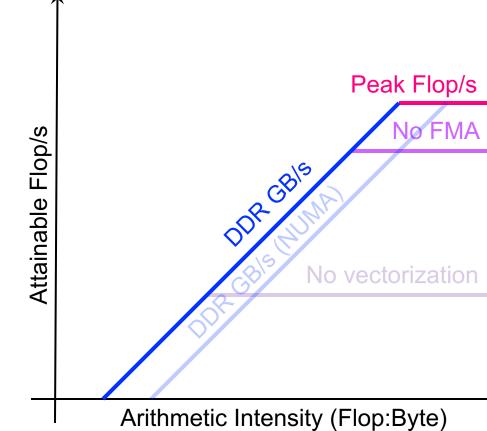

### **Non-Uniform Memory Access (NUMA)**

- In a shared memory, any thread can read any memory location

- However, memory bandwidth and latency can vary (NUMA)

- Consider array double X[N]; Ο

- If naively allocated, all data is placed on Ο socket 0

- Latency/bandwidth to element x[i] is Ο different for thread 3 and thread 4

- Socket 0's memory bandwidth is highly Ο contended while socket 1's is underutilized

### **Non-Uniform Memory Access (NUMA)**

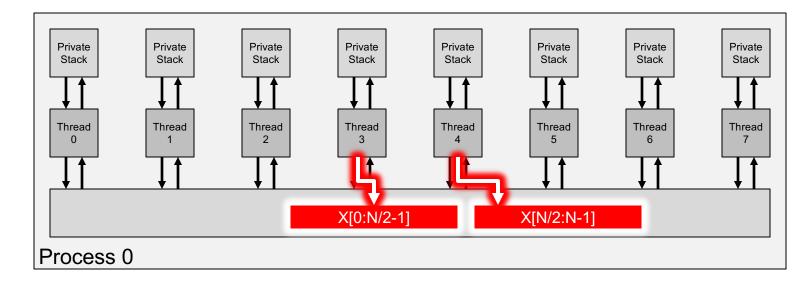

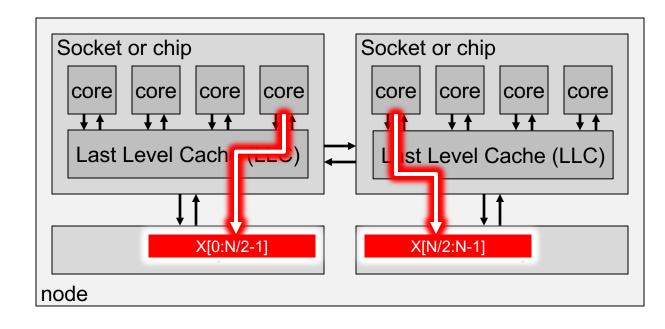

- Allocate data based on how we intend to access it

- Rectify this NUMA effect via *first* touch initialization

- Pages are allocated with affinity to the Ο core that first touched the data

- Parallelizing the initialization transparently Ο partitions the array among NUMA nodes

- n.b. This only works on the first allocation Ο of this memory page (subsequent free/malloc corrupt the process)

- **Explicit thread affinity is imperative** Ο

### **Non-Uniform Memory Access (NUMA)**

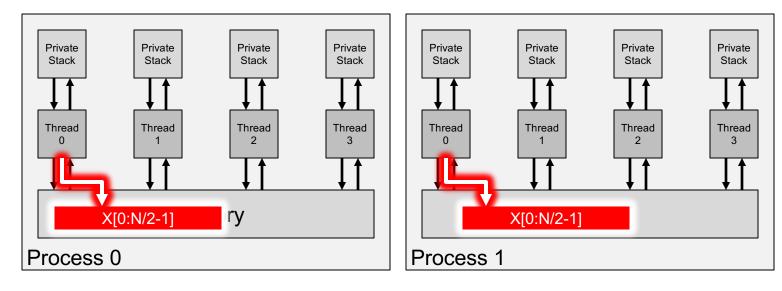

- Simplest solution is to run at least one process per NUMA node

- All data for that process is allocated on Ο the numa node with affinity to its cores

- All data access are restricted to that  $\bigcirc$ NUMA node

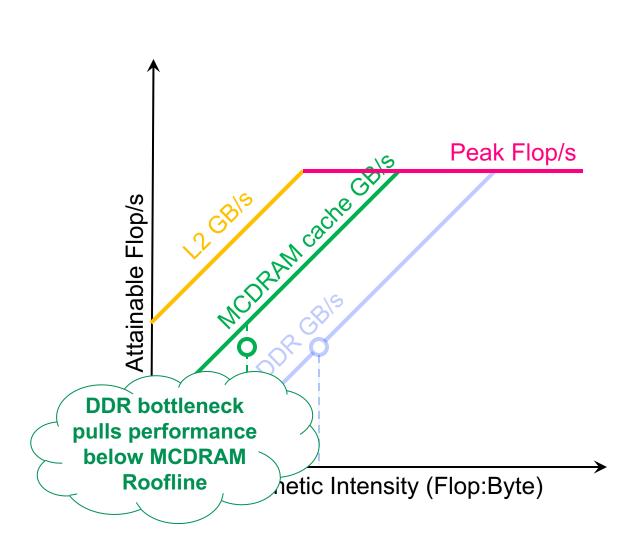

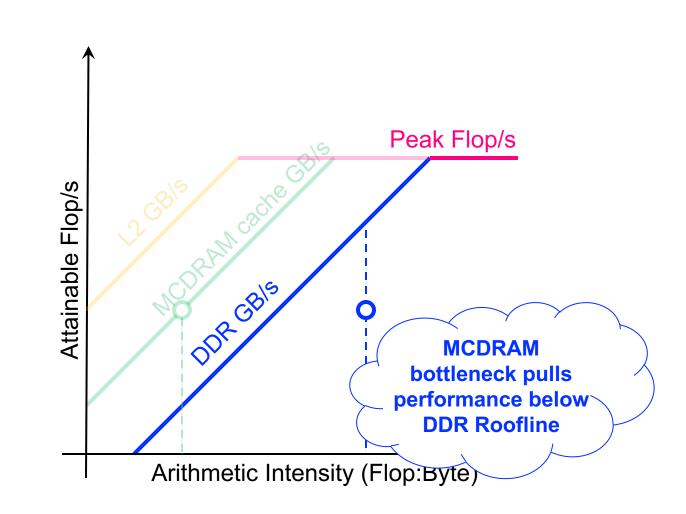

### **Memory/Cache Capacity Contention**

- Each thread or process exerts some pressure on the cache (on-chip) L1/L2 or off-chip MCDRAM/HBM memory).

- As thread/process-concurrency increases, the requisite active working set can exceed cache capacity

- When this happens, capacity misses manifest, data movement increases (even if perfectly Ο computationally load balanced), and **performance can plummet**.

- If this happens in MCDRAM or HBM caches, we run at DDR speeds or Nvlink speeds. Ο

- To rectify this, we often tile or block loops so that the per-thread working set remains sufficiently small.

### **Memory/Cache Bandwidth Contention**

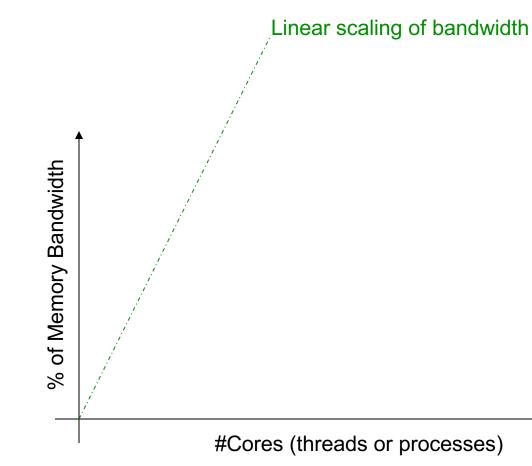

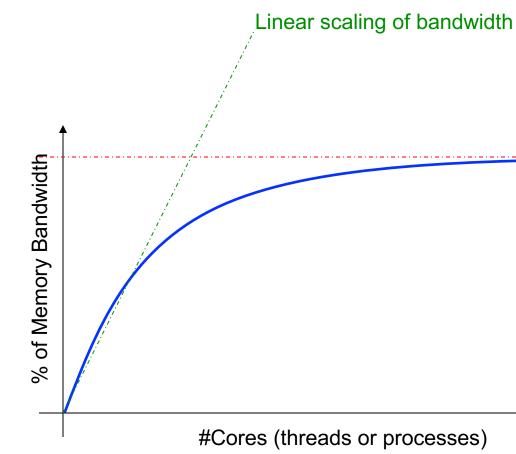

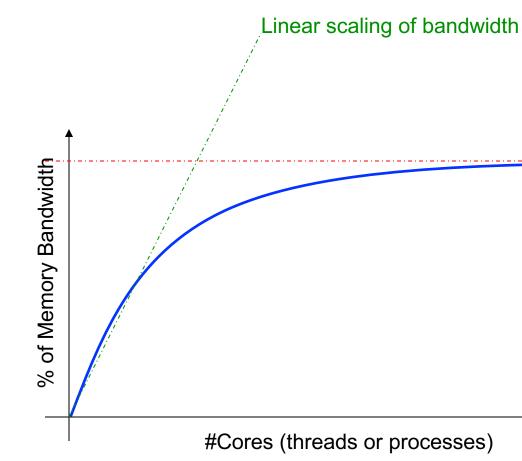

- There is less memory bandwidth than all cores could consume

- 1 core can drive >10GB/s of memory Ο bandwidth

- 16 cores (e.g. 1P HSW) could drive >160 Ο

### **Memory/Cache Bandwidth Contention**

- There is less memory bandwidth than all cores could consume

- 1 core can drive >10GB/s of memory Ο bandwidth

- 16 cores (e.g. 1P HSW) could drive >160 Ο

- Socket only has 50GB/s available. Ο

- memory bandwidth has become a Ο bottleneck

- A similar effect can emerge on LLC or Ο **MCDRAM** caches

100%

### **Memory/Cache Bandwidth Contention**

- There is less memory bandwidth than all cores could consume

- 1 core can drive >10GB/s of memory Ο bandwidth

- 16 cores (e.g. 1P HSW) could drive >160 Ο

- Socket only has 50GB/s available. Ο

- memory bandwidth has become a Ο bottleneck

- A similar effect can emerge on LLC or Ο **MCDRAM** caches

- "Flops are Free"

- bottleneck or opportunity? Ο

100%

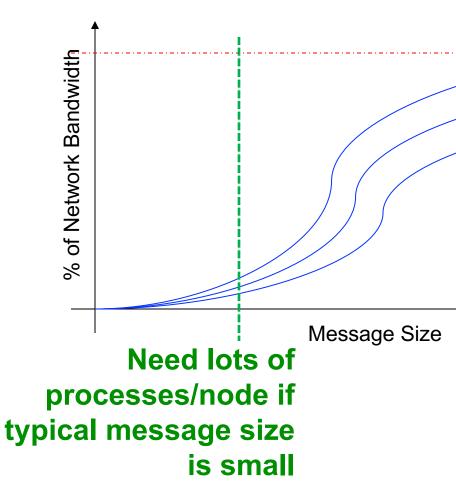

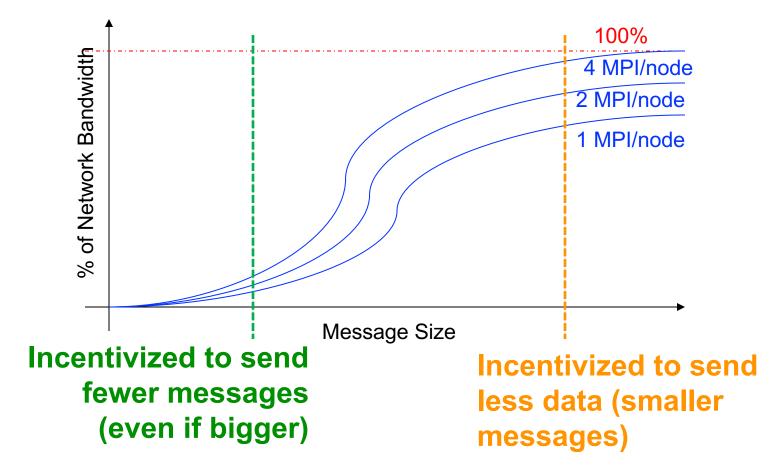

### **Network Performance**

- Each message sent via MPI incurs some non-zero overhead (and latency)

- We can proxy message time as: time = overhead + size/bandwidth

- As such, network utilization...

- = size / (overhead\*bandwidth + size)

- = (overhead\*bandwidth/size + 1)<sup>-1</sup>

Latency-Bandwidth Product

### **Network Performance**

- Each message sent via MPI incurs some non-zero overhead (and latency)

- We can proxy message time as: time = overhead + size/bandwidth

- As such, network utilization...

- = size / (overhead\*bandwidth + size)

- = (overhead\*bandwidth/size + 1)<sup>-1</sup>

Latency-Bandwidth Product

### **Network Contention**

- We can saturate different aspects of the network...

- Injection Bandwidth

- $\circ$   $\,$  nodes cannot inject data faster into the network

- e.g. broadcasts or large messages

- Ejection Bandwidth

- $\circ$   $\$  node cannot eject data from the network fast enough

- o e.g. reductions (single node must receive data from all other nodes)

### Bisection Bandwidth

- Bandwidth (links) connecting conceptual partitions of the network

- Artifact of the topology (architecture) of the network

- Job placement (and decomposition) can mitigate this

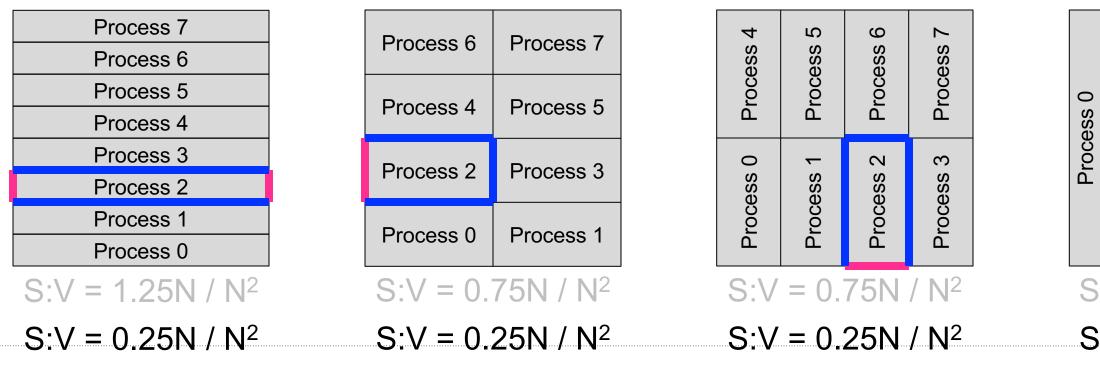

### Surface:Volume

- When we decompose a problem among processes, we must do so in a manner that...

- Minimizes the number of messages (recall overhead per message) Ο

- Minimizes the surface:volume ratio (i.e. ratio of MPI data movement : local flops) Ο

- Consider 8-way MPI parallelization of a PDE on a NxN structured grid...

| Process 7 |

|-----------|

| Process 6 |

| Process 5 |

| Process 4 |

| Process 3 |

| Process 2 |

| Process 1 |

| Process 0 |

|           |

$S:V = 2.25N / N^2$

| $S \cdot V = 1.5 \text{ N} / \text{N}^2$ |           |  |

|------------------------------------------|-----------|--|

| Process 0 Process 1                      |           |  |

| Process 2                                | Process 3 |  |

| Process 4                                | Process 5 |  |

| Process 6                                | Process 7 |  |

| Process 4          | Process 5 | Process 6 | Process 7 |

|--------------------|-----------|-----------|-----------|

| Process 0          | Process 1 | Process 2 | Process 3 |

| $S:V = 1.5N / N^2$ |           |           |           |

0

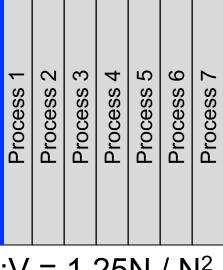

### S 9 $\sim$ З 4 Process Process Process Process Process Process Process $S:V = 2.25N / N^2$

# Surface:Volume

- On a multicore node, think about how much data is off node exchanges vs. on-node exchanges.

- On-node exchanges should be faster (DRAM BW >> Network BW)

- Different off-node surface:volume ratios leads to load imbalance.

| Process 7           | D  |

|---------------------|----|

| Process 6           | FI |

| Process 5           | D  |

| Process 4           |    |

| Process 3           | D  |

| Process 2           | FI |

| Process 1           | D  |

| Process 0           |    |

| $S:V = 1.25N / N^2$ | S  |

|                     |    |

| Process 6           | Process 7 |  |

|---------------------|-----------|--|

| Process 4           | Process 5 |  |

| Process 2           | Process 3 |  |

| Process 0 Process 1 |           |  |

| $S:V = 0.75N / N^2$ |           |  |

| Process 4           | Process 5 | Process 6 | Process 7 |

|---------------------|-----------|-----------|-----------|

| Process 0           | Process 1 | Process 2 | Process 3 |

| $S:V = 0.75N / N^2$ |           |           |           |

### $S:V = 1.25N / N^2$

# Surface:Volume

- On a multicore node, think about how much data is off node exchanges vs. on-node exchanges.

- On-node exchanges should be faster (DRAM BW >> Network BW)

- Different off-node surface:volume ratios leads to load imbalance.

|--|

### $S:V = 1.25N / N^2$

$S:V = 0.25N / N^2$

### Little's Law Redux...

- Recast latency-bandwidth product for OMP/CUDA overheads & flop/s...

- Haswell (Xeon CPU):

- 100 GB/s, 1.3 Tflop/s, ~1us OMP overhead Ο

- Can't hit peak bandwidth on any kernel that moves less than 100KB 0

- Can't hit peak flops on any kernel that does less than 1M FP operations 0

- KNL (Xeon Phi Manycore):

- 400 GB/s, 2.5 Tflop/s, ~5us OMP overhead Ο

- Can't hit peak bandwidth on any kernel that moves less than 2MB Ο

- Can't hit peak flops on any kernel that does less than 13M FP operations Ο

- Volta GPU:

- 800 GB/s, 7 Tflop/s, ~20us CUDA launch overhead Ο

- Can't hit peak bandwidth on any kernel that moves less than 16MB Ο

- Can't hit peak flops on any kernel that does less than 140M FP operations Ο

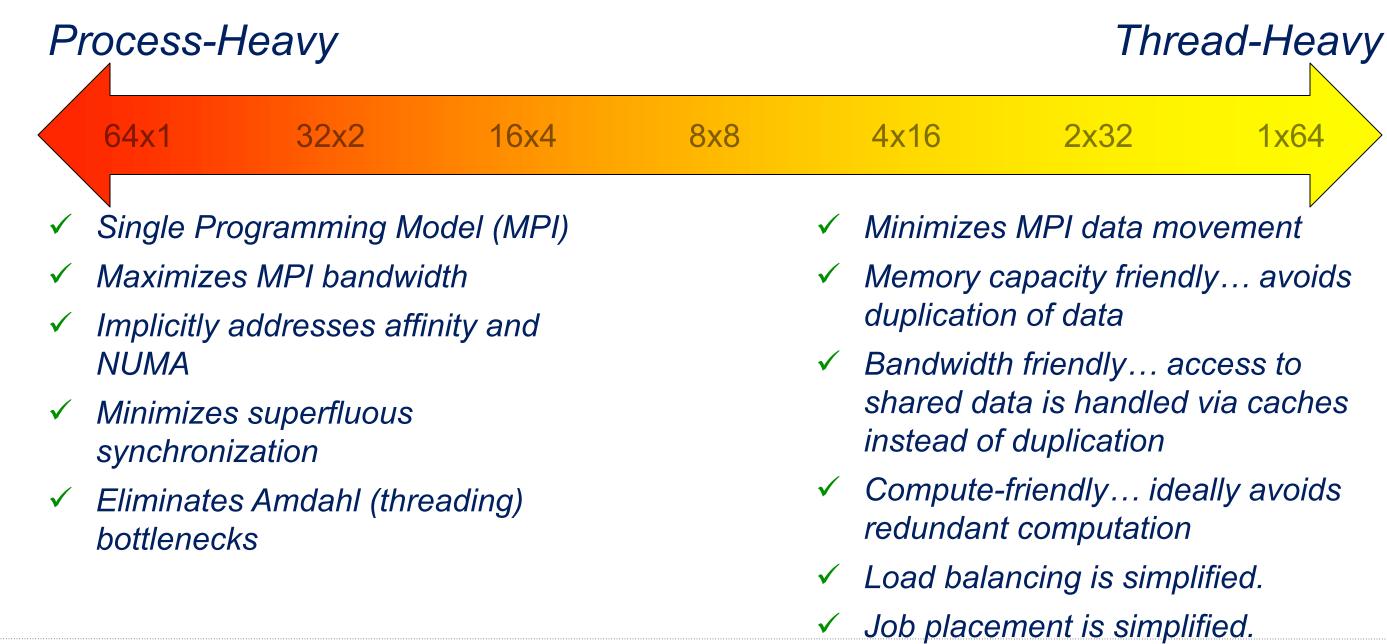

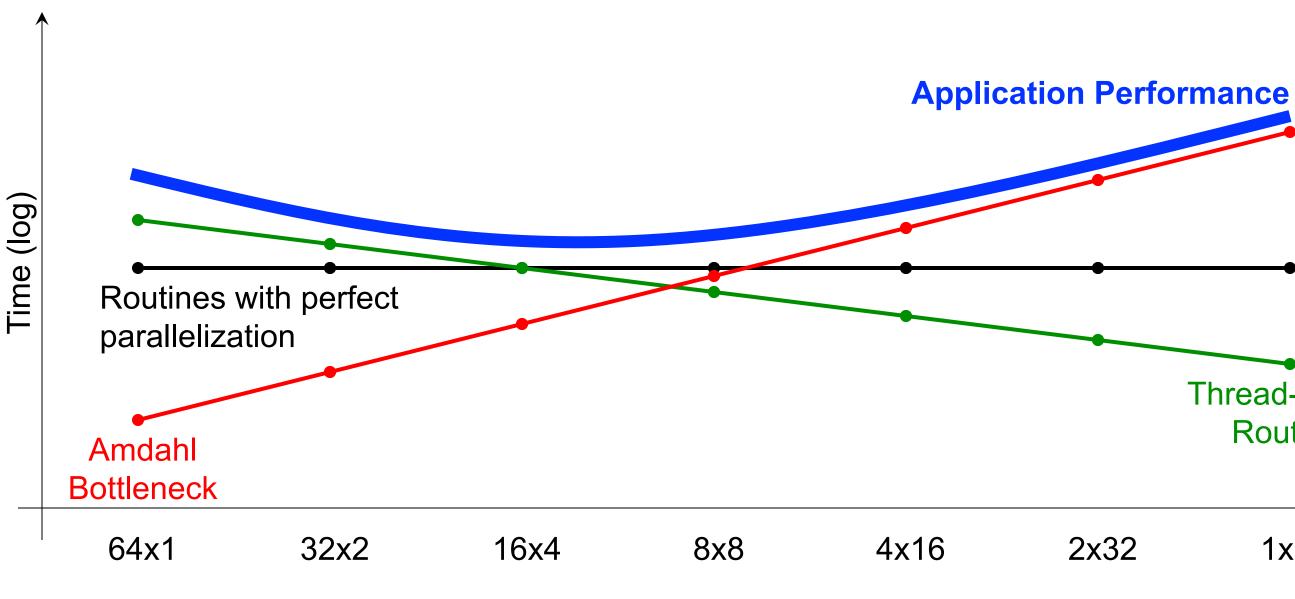

### **Trading Process Concurrency for Thread Concurrency**

### **Trading Process Concurrency for Thread Concurrency**

### Thread-friendly **Routines**

### 1x64

**BERKELEY LAB**

CE BERKELEY NATIONAL LABORATORY

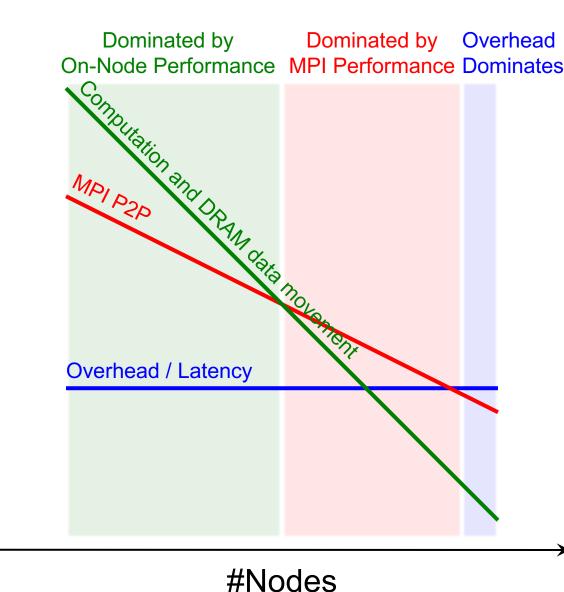

# Performance and Scalability

### **Strong vs. Weak Scaling**

### **Strong Scaling:**

- Global problem sized remains fixed Ο

- Scale the number of nodes (per-node problem size decreases with #nodes) Ο

- network/threading overheads/latencies quickly dominate run time Ο

### Weak Scaling:

- Global problem size grows proportional to the number of nodes Ο

- Scale the number of nodes (per-node problem size remains fixed) Ο

- Generally keeps network/ threading overheads/latencies in check Ο

- Superlinear algorithms become extremely time consuming (Dense LU takes a day) Ο

- Not amenable to all computational domains Ο

- Corollary: scale per-node problem size with per-node throughput Ο (e.g. when moving from a 2P Xeon to a 6xGPU node)

# **Strong Scaling Example**

by Component

Time

- e.g. PDE on a structured grid

- Domain decomposition produces an initially favorable surface:volume ratio (MPI:local)

- Strong scaling quickly reduces the volume.

- Surface (e.g. MPI) quickly dominates.

- If scaling continues, overheads can dominate

**BERKELEY LAB**

ENCE BERKELEY NATIONAL LABORATORY

# Performance Models

### Why Use Performance Models or Tools?

- Identify performance bottlenecks

- Motivate software optimizations

- **Determine when we're done optimizing**

- Assess performance relative to machine capabilities ullet

- Motivate need for algorithmic changes ۲

- Predict performance on future machines / architectures

- Sets realistic expectations on performance for future procurements ۲

- Used for HW/SW Co-Design to ensure future architectures are well-suited for the computational needs of today's applications.

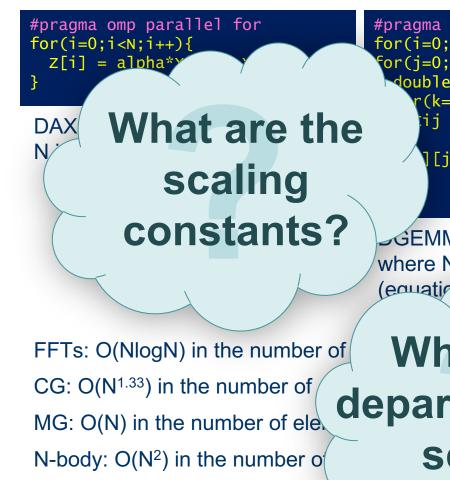

# **Computational Complexity**

- Assume run time is correlated with the number of operations (e.g. FP ops)

- Users define parameterize their algorithms, solvers, kernels

- Count the number of operations as a function of those parameters

- Demonstrate run time is correlated with those parameters

```

#pragma omp parallel for

for(i=0;i<N;i++){

For(j=0;j<N;j++){

double Cij=0;

r(k=0;k<N;k++){

ij += A[i][k] * B[k][j];

][j] = sum;

```

GEMM: O(N<sup>3</sup>) complexity where N is the number of rows (equation

### Why did we depart from ideal scaling?

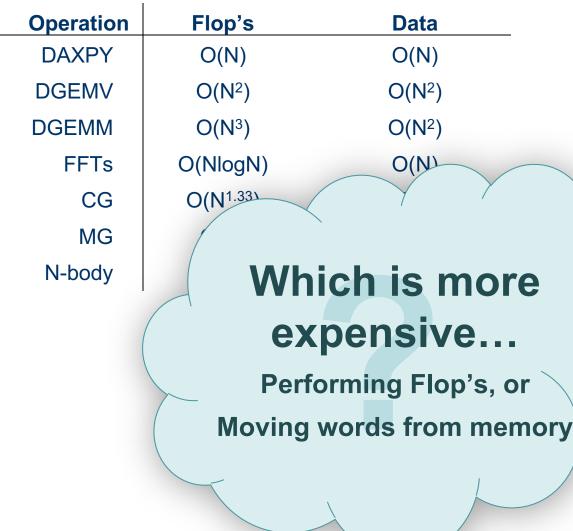

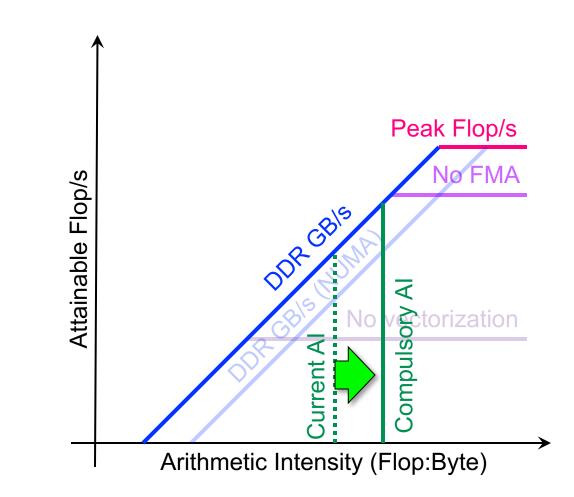

# **Data Movement Complexity**

- Assume run time is correlated with the amount of data accessed (or moved)

- Easy to calculate amount of data accessed... count array accesses

- Data moved is more complex as it requires understanding cache behavior...

- Compulsory<sup>1</sup> data movement (array sizes) is a good initial guess...

- ... but needs refinement for the effects of finite cache capacities

<sup>1</sup>Hill et al, "Evaluating Associativity in CPU Caches", IEEE Trans. Comput., 1989.

### expensive... Performing Flop's, or

Data

O(N)

$O(N^2)$

$O(N^2)$

O(N)

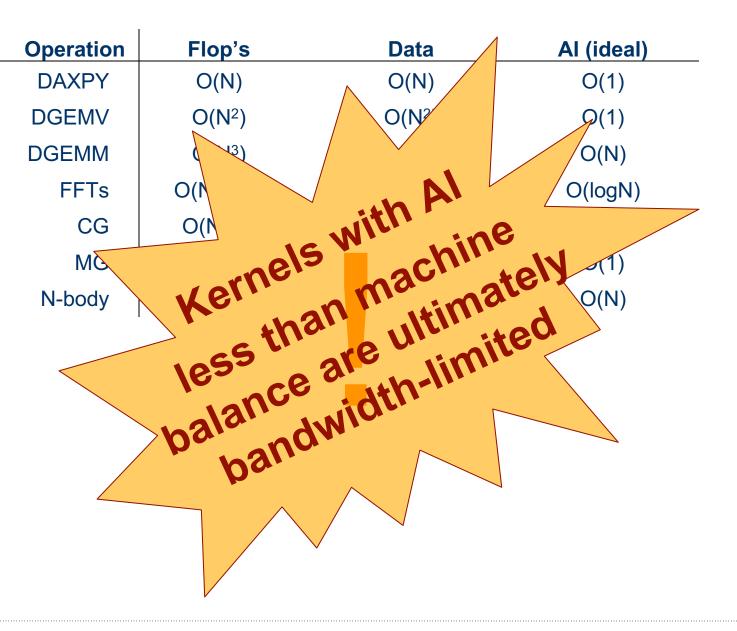

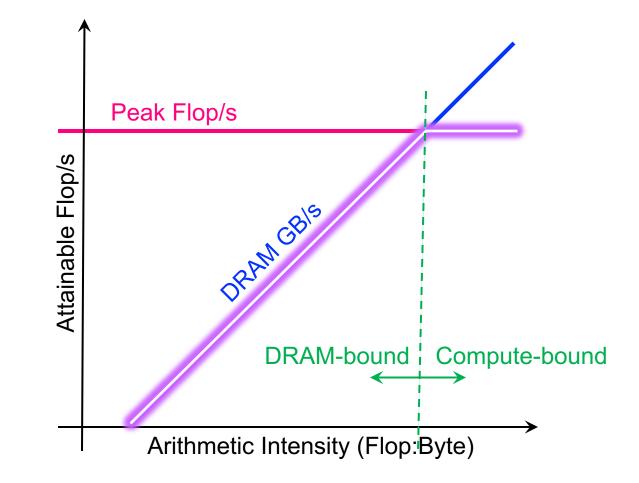

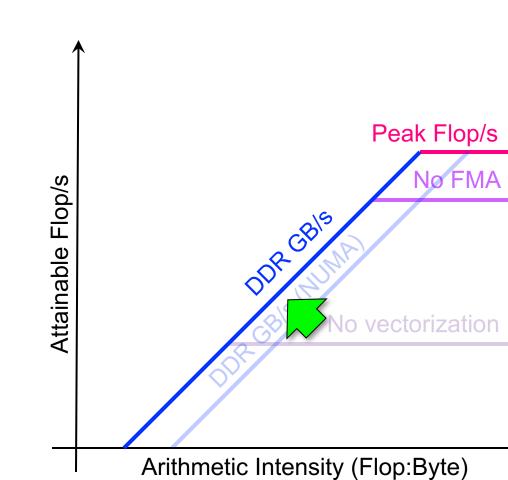

### **Machine Balance and Arithmetic Intensity**

- Data movement and computation can operate at different rates

- We define machine balance as the ratio of...

Balance = Peak DP Flop/s Peak Bandwidth

...and arithmetic intensity as the ratio of...

AI = Flop's Performed Data Moved

### **Distributed Memory Performance Modeling**

- In distributed memory, one communicates by sending messages between processors.

- Messaging time can be constrained by several components...

- Overhead (CPU time to send/receive a message)

- Latency (time message is in the network; can be hidden)

- Message throughput (rate at which one can send small messages... messages/second)

- Bandwidth (rate one can send large messages... GBytes/s)

- Bandwidths and latencies are further constrained by the interplay of network architecture and contention

- Distributed memory versions of our algorithms can be differently stressed by these components depending on N and P (#processors)

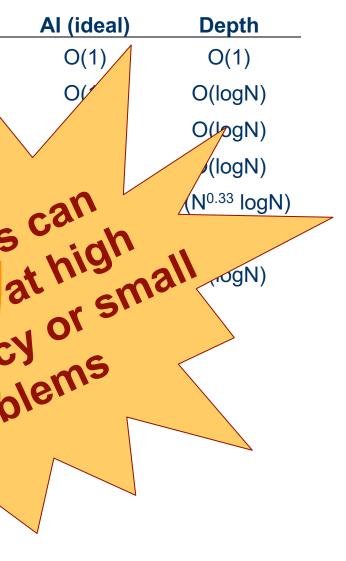

# **Computational Depth**

- Imagine a world of infinite parallelism & bandwidth, but finite latencies

- We can classify algorithms by depth (max depth of the algorithm's dependency chain)

- For iterative algorithms, this is product of iterations and depth per iteration

| Flop's                | Data                                                                                         |

|-----------------------|----------------------------------------------------------------------------------------------|

| O(N)                  | O(N)                                                                                         |

| O(N <sup>2</sup> )    | O(N <sup>2</sup> )                                                                           |

| O(N <sup>3</sup> )    | O(N <sup>2</sup> )                                                                           |

| O(NlogN               | O(N                                                                                          |

| O(N <sup>1.33</sup> ) | N1                                                                                           |

| O(N)                  | - 95                                                                                         |

|                       | lerheads                                                                                     |

|                       | inate<br>minate<br>ncurrent<br>prot                                                          |

|                       | O(N)<br>O(N <sup>2</sup> )<br>O(N <sup>3</sup> )<br>O(NlogN<br>O(N <sup>1.33</sup> )<br>O(N) |

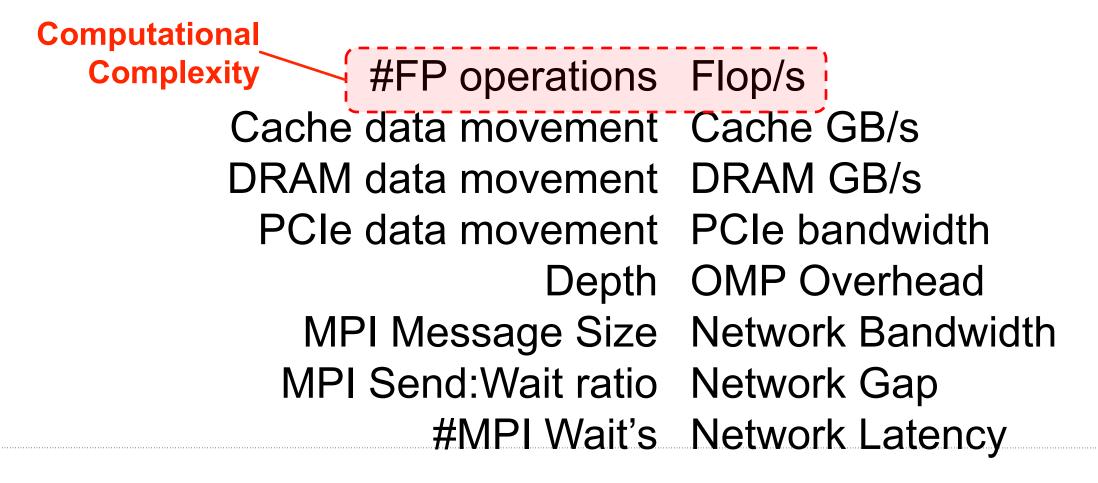

- Many different components can contribute to kernel run time.

- Some are characteristics of the application, some are characteristics of the machine, and some are both (memory access pattern + caches).

**#FP operations** Flop/s Cache data movement Cache GB/s DRAM data movement DRAM GB/s PCIe data movement PCIe bandwidth Depth OMP Overhead MPI Message Size Network Bandwidth MPI Send: Wait ratio Network Gap #MPI Wait's Network Latency

Can't think about all these terms all the time for every application...

Because there are so many components, performance models often conceptualize the system as being dominated by one or more of these components.

> Roofline **#FP operations** Flop/s Model Cache data movement Cache GB/s DRAM data movement DRAM GB/s PCIe data movement PCIe bandwidth Depth OMP Overhead MPI Message Size Network Bandwidth MPI Send: Wait ratio Network Gap #MPI Wait's Network Latency

Williams et al, "Roofline: An Insightful Visual Performance Model For Multicore Architectures",

Because there are so many components, performance models often conceptualize the system as being dominated by one or more of these components.

> **#FP operations** Flop/s Cache data movement Cache GB/s DRAM data movement DRAM GB/s PCIe data movement PCIe bandwidth Depth OMP Overhead MPI Message Size Network Bandwidth MPI Send: Wait ratio Network Gap LogP #MPI Wait's Network Latency

Because there are so many components, performance models often conceptualize the system as being dominated by one or more of these components.

> **#FP operations** Flop/s Cache data movement Cache GB/s DRAM data movement DRAM GB/s PCIe data movement PCIe bandwidth Depth OMP Overhead MPI Message Size Network Bandwidth MPI Send: Wait ratio Network Gap #MPI Wait's Network Latency

Alexandrov, et al, "LogGP: incorporating long messages into the LogP model - one step closer

towards a realistic model for parallel computation", SPAA, 1995.

Because there are so many components, performance models often conceptualize the system as being dominated by one or more of these components.

**#FP operations** Flop/s Cache data movement Cache GB/s ink about w odel to use DRAM data movement DRAM GR/P PCIe data movement PCIe band LogCA Depth OMP C Th MPI Message Size Network B MPI Send: Wait ratio Network Gan #MPI Wait's Network Latercy

Bin Altaf et al, "LogCA: A High-Level Performance Model for Hardware Accelerators", ISCA,

**BERKELEY LAB**

ELEY NATIONAL LABORATORY

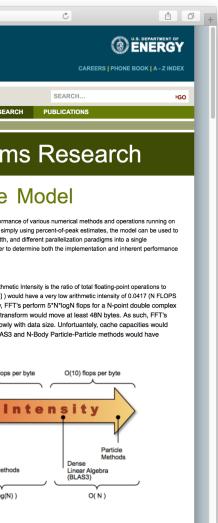

# Introduction to the Roofine Mode

### **Performance Models / Simulators**

- Historically, many performance models and simulators tracked latencies to predict performance (i.e. counting cycles)

- The last two decades saw a number of latency-hiding techniques...

- Out-of-order execution (hardware discovers parallelism to hide latency)

- HW stream prefetching (hardware speculatively loads data)

- Massive thread parallelism (independent threads satisfy the latency-bandwidth product) ٠

- Effective latency hiding has resulted in a shift from a latency-limited computing regime to a **throughput-limited computing regime**

# **Roofline Model**

61

- **Roofline Model** is a throughput-oriented performance model...

- Tracks rates not times

- Augmented with Little's Law (concurrency = latency\*bandwidth)

- Independent of ISA and architecture (applies to CPUs, GPUs, Google TPUs<sup>1</sup>, etc...)

|                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ESEARCH                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                           | ERFORMANCE AND ALGORITHMS RESE                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                          |

| Perfor                                                                                                                                                    | mance and                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Algorithm                                                                                                                                                                                                                                                                                                                                                                                                |

| PERFORMANCE<br>AND<br>ALGORITHMS<br>RESEARCH<br>Auto-tuning<br>BeBOP<br>EDGAR<br>HipGISAXS<br>HiPGMG<br>Roofline<br>SciDAC<br>TOP500<br>Previous Projects | Recoffice Pee<br>Roofine is a visually intuitive performan<br>multicore, manycore, or accelerator prov<br>assess the quality of attained performan<br>performance figure. One can examine th<br>imitations:<br>Anticon Peerformance Pehrind the Roofine<br>total data movement (bytes). A BLAS-1<br>/24N Bytes) and would be independen<br>transform. If out of place on a write a<br>would have an arithmetic intensity of<br>limit FFT arithmetic intensity grow very quickly | nce model used to bound the perform<br>cessor architectures. Rather than sin<br>nce by combining locality, bandwidth,<br>he resultant Roofline figure in order t<br>e model is Arithmetic Intensity. Arithm<br>vector-vector increment (x[]+=y[])<br>ht of the vector size. Conversely, F<br>illocate cache architecture, the fra<br>0.104*logN and would grow slow<br>sp2 flops per byte. Finally, BLAS |

| Facebook<br>Google+                                                                                                                                       | 0.1-1.0 flops pe<br>A r i<br>SpMV<br>BLAS1,2<br>Stencils (PDEs)<br>Latice                                                                                                                                                                                                                                                                                                                                                                                                       | ithmetic I                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                           | O(1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | O( log(                                                                                                                                                                                                                                                                                                                                                                                                  |

https://crd.lbl.gov/departments/computer-science/PAR/research/roofline

**Roofline Model**

- One could hope to always attain peak performance (Flop/s)

- However, finite locality (reuse) and bandwidth limit performance.

- Assume:

- Idealized processor/caches

- Cold start (data in DRAM)

**#FP ops / Peak GFlop/s #Bytes / Peak GB/s** Time = max <

- One could hope to always attain peak performance (Flop/s)

- However, finite locality (reuse) and bandwidth limit performance.

- Assume:

- Idealized processor/caches

- Cold start (data in DRAM)

### 1 / Peak GFlop/s #Bytes / #FP ops / Peak GB/s Time = max **#FP ops**

- One could hope to always attain peak performance (Flop/s)

- However, finite locality (reuse) and bandwidth limit performance.

- Assume:

- Idealized processor/caches

- Cold start (data in DRAM)

# Peak GFlop/s (#FP ops / #Bytes) \* Peak GB/s #FP ops Time :

- One could hope to always attain peak performance (Flop/s)

- However, finite locality (reuse) and bandwidth limit performance.

- Assume:

- Idealized processor/caches

- Cold start (data in DRAM)

Note, Arithmetic Intensity (AI) = Flops / Bytes (as presented to DRAM)

- Plot Roofline bound using Arithmetic Intensity as the x-axis

- Log-log scale makes it easy to doodle, extrapolate performance along Moore's Law, etc...

- Kernels with AI less than machine balance are ultimately DRAM bound (we'll refine this later...)

# **Roofline Example #1**

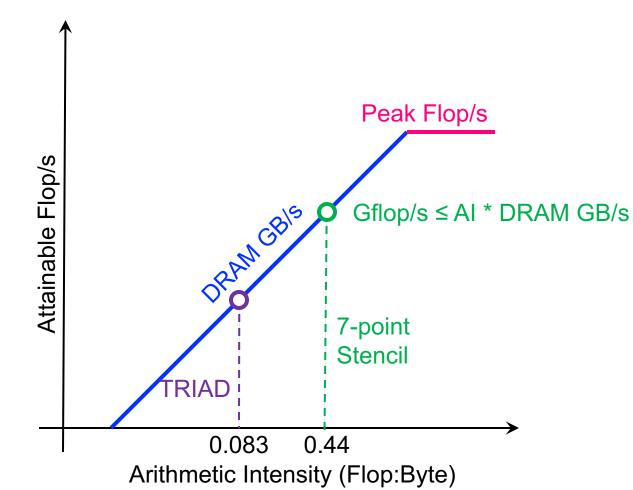

- Typical machine balance is 5-10 flops per byte... 40-80 flops per double to exploit compute capability ٠ Artifact of technology and money • Attainable Flop/s **Unlikely to improve** ٠ DRAMGBIS Consider STREAM Triad... #pragma omp parallel for for(i=0;i<N;i++){</pre> TRIAD Z[i] = X[i] + alpha\*Y[i];0.083

- 2 flops per iteration ٠

- Transfer 24 bytes per iteration (read X[i], Y[i], write Z[i])

- AI = 0.083 flops per byte == Memory bound ٠

### $Gflop/s \leq AI * DRAM GB/s$

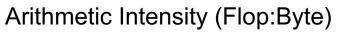

# **Roofline Example #2**

### Conversely, 7-point constant coefficient stencil...

- 7 flops •

- 8 memory references (7 reads, 1 store) per point •

- Cache can filter all but 1 read and 1 write per point

- AI = 0.44 flops per byte == memory bound, •

### but 5x the flop rate

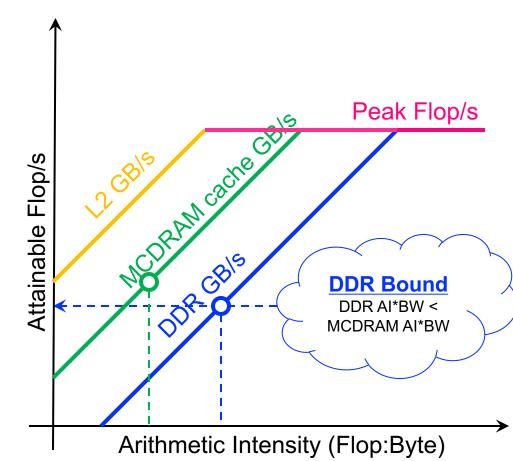

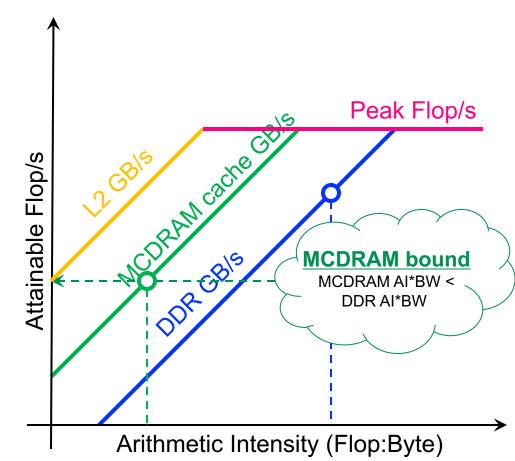

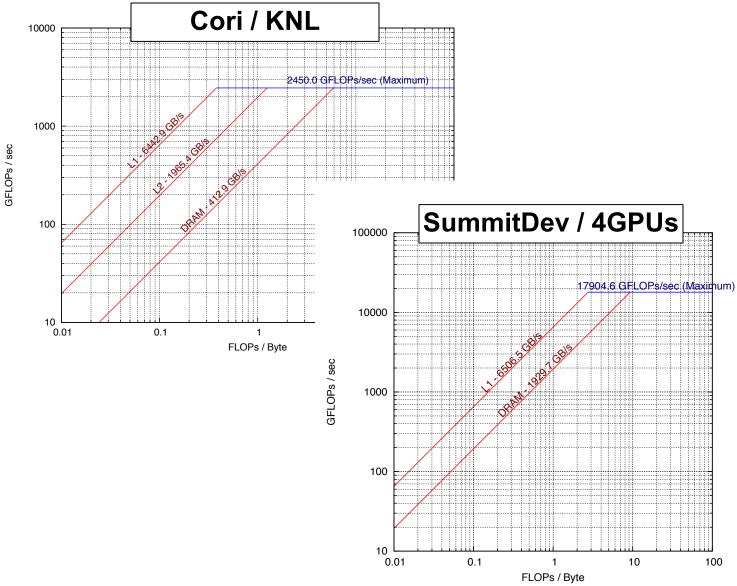

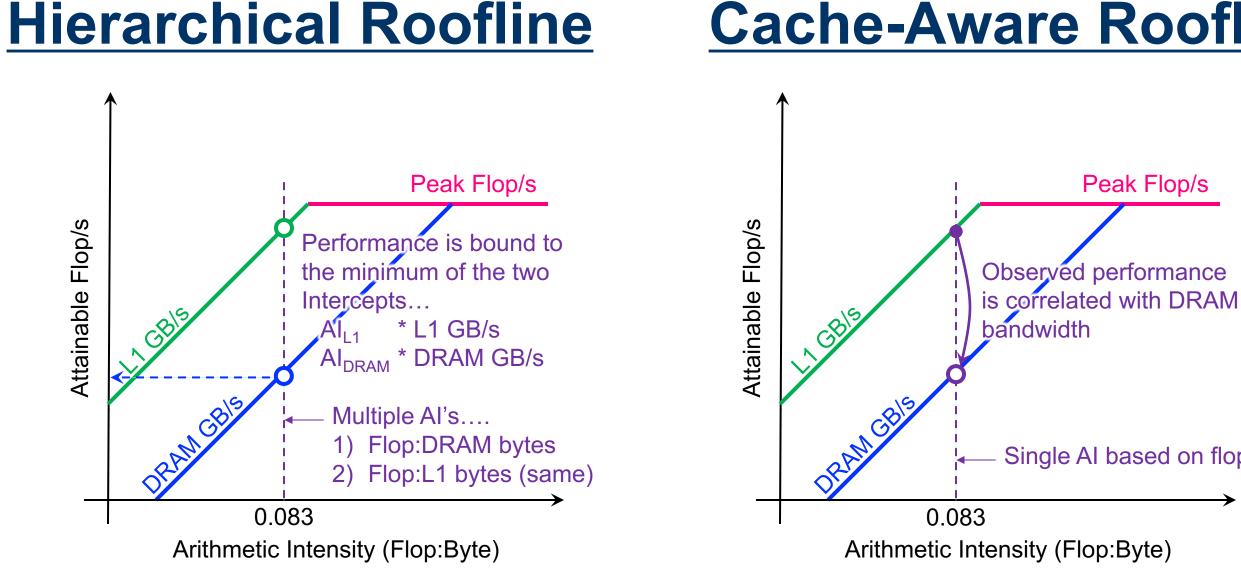

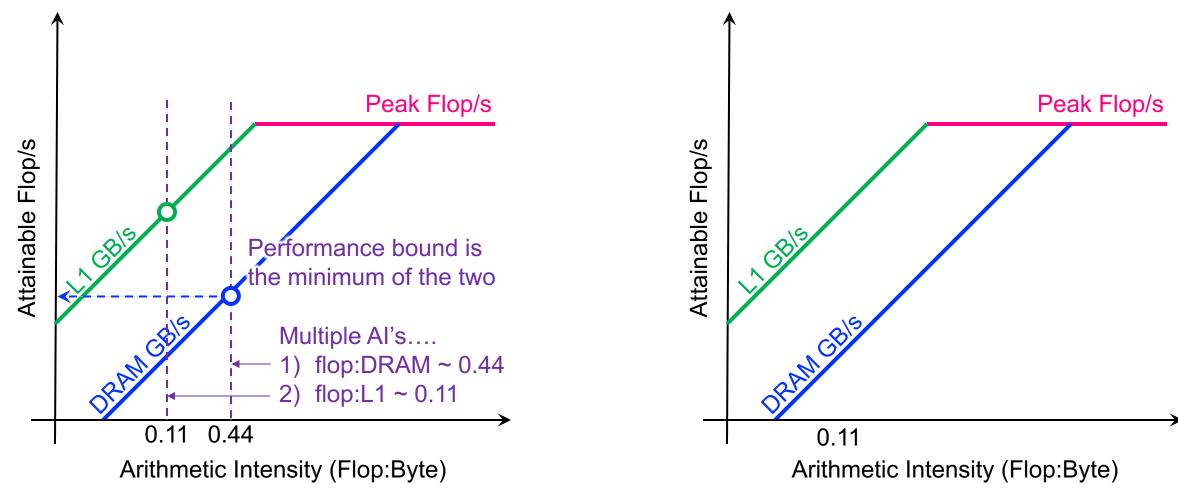

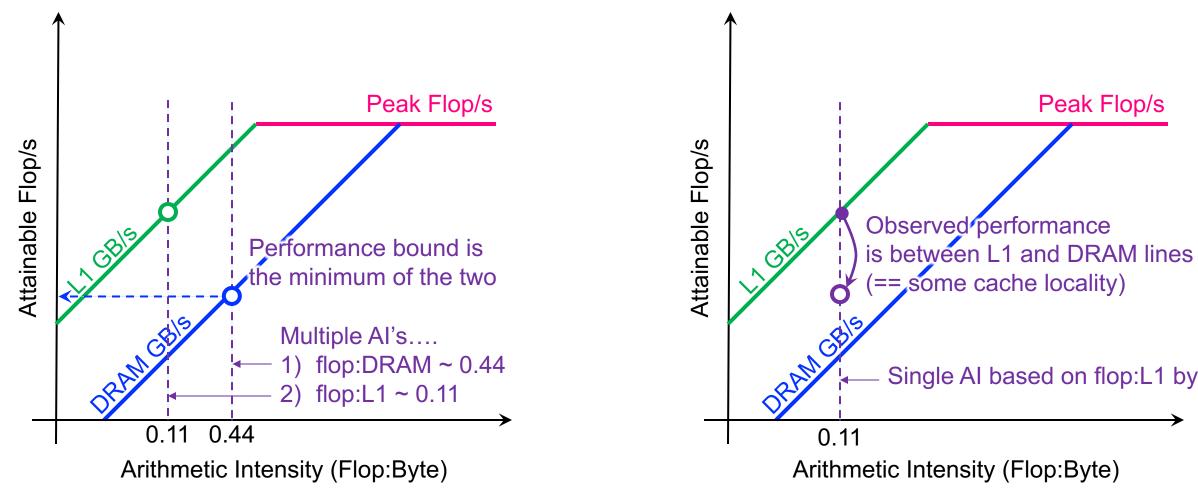

- Real processors have multiple levels of memory

- Registers

- L1, L2, L3 cache

- MCDRAM/HBM (KNL/GPU device memory)

- DDR (main memory)

- NVRAM (non-volatile memory)

- Applications can have locality in each level

- Unique data movements imply unique Al's

- Moreover, each level will have a unique bandwidth

- Construct superposition of Rooflines...

- Measure a bandwidth

- Measure AI for each level of memory

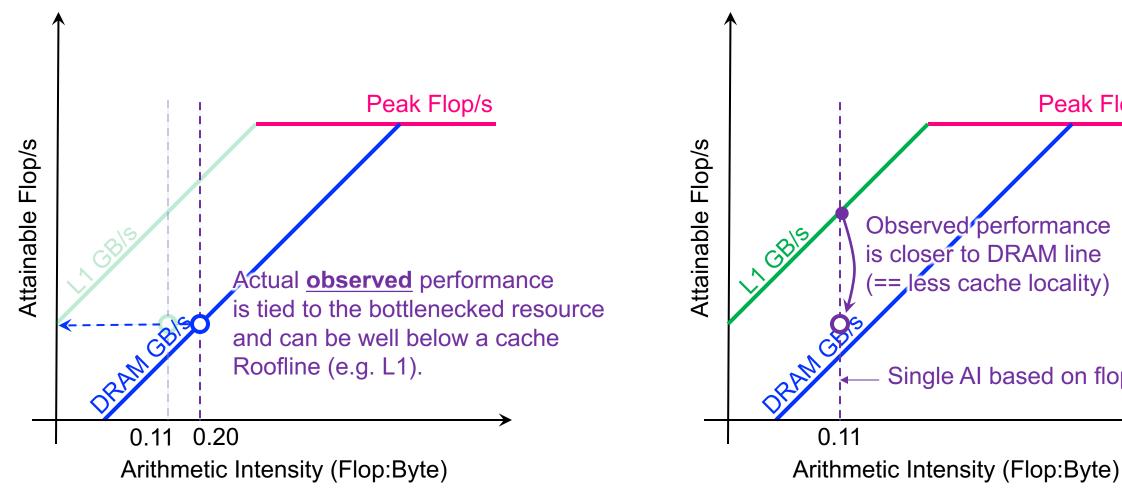

- Although an loop nest may have multiple Al's and multiple bounds (flops, L1, L2, ... DRAM)...

- ... performance is bound by the minimum

- Construct superposition of Rooflines...

- Measure a bandwidth

- Measure AI for each level of memory

- Although an loop nest may have multiple Al's and multiple bounds (flops, L1, L2, ... DRAM)...

- ... performance is bound by the minimum

- Construct superposition of Rooflines...

- Measure a bandwidth

- Measure AI for each level of memory

- Although an loop nest may have multiple Al's and multiple bounds (flops, L1, L2, ... DRAM)...

- ... performance is bound by the minimum

# **Hierarchical Roofline**

- Construct superposition of Rooflines...

- Measure a bandwidth

- Measure AI for each level of memory

- Although an loop nest may have multiple Al's and multiple bounds (flops, L1, L2, ... DRAM)...

- ... performance is bound by the minimum

BERKELEY NATIONAL LABORATORY

# Roofline Model: In-Core Effects

# Data, Instruction, Thread-Level Parallelism...

Modern CPUs use several techniques to increase per core Flop/s

### **Fused Multiply Add**

- $w = x^*y + z$  is a common idiom in kine algebra

- lacksquareCOR se a ado (FMA)

- ∧ J chains the mutiply and add in a single pipeline so that it can complete FMA/cycle

### **Vector Instructions**

- Many HPC codes apply the same operation to a vector of elements

- Vendors provide vector instructions that apply the same operation to 2, 4, 8, 16 elements...

- x [0:7] \*y [0:7] + z [0:7]

- Vector FPUs complete 8 vector operations/cycle

- is substantial.

- increase GHz

- FP bandwidth

### **Deep Pipelines**

The hardware for a FMA

Breaking a single FMA up into several smaller operations and pipelining them allows vendors to

Little's Law applies... need FP Latency \* independent instructions

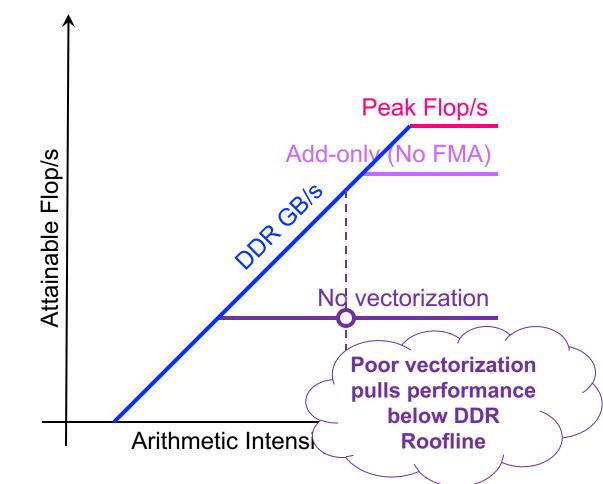

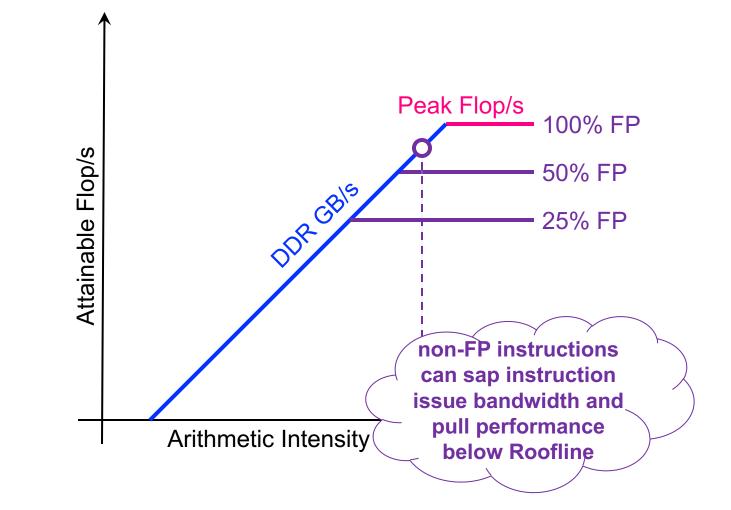

## Data, Instruction, Thread-Level Parallelism...

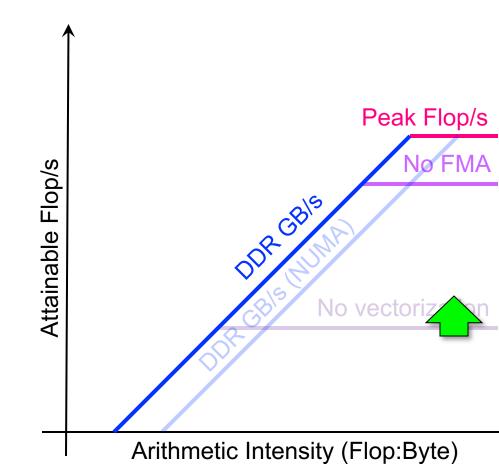

- If every instruction were an ADD (instead of FMA), performance would drop by 2x on KNL or 4x on Haswell

- Similarly, if one had no vector instructions, performance would drop by another 8x on KNL and 4x on Haswell

- FP Divides can be even worse.

- Lack of threading will reduce performance by 64x on KNL.

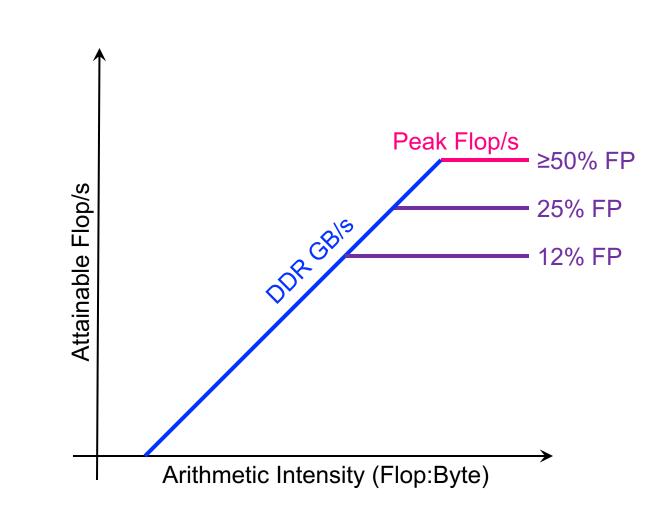

## **Superscalar vs. instruction mix**

- Define in-core ceilings based on instruction mix...

- e.g. Haswell

- 4-issue superscalar ullet

- Only 2 FP data paths ٠

- Requires 50% of the instructions to be FP to get peak performance

# Superscalar vs. instruction mix

- Define in-core ceilings based on instruction mix...

- e.g. Haswell

- 4-issue superscalar

- Only 2 FP data paths

- Requires 50% of the instructions to be FP to get peak performance

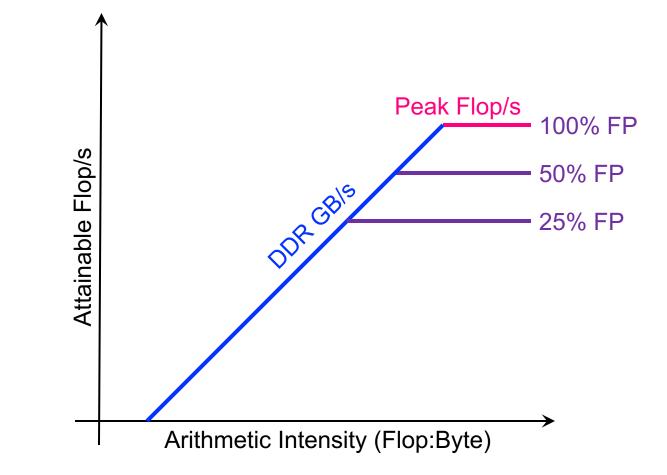

- e.g. KNL

- 2-issue superscalar

- 2 FP data paths

- Requires 100% of the instructions to be FP to get peak performance

# Superscalar vs. instruction mix

- Define in-core ceilings based on instruction mix...

- e.g. Haswell

- 4-issue superscalar

- Only 2 FP data paths

- Requires 50% of the instructions to be FP to get peak performance

- e.g. KNL

- 2-issue superscalar

- 2 FP data paths

- Requires 100% of the instructions to be FP to get peak performance

BERKELEY NATIONAL LABORATORY

# Roofline Model: Cache Effects

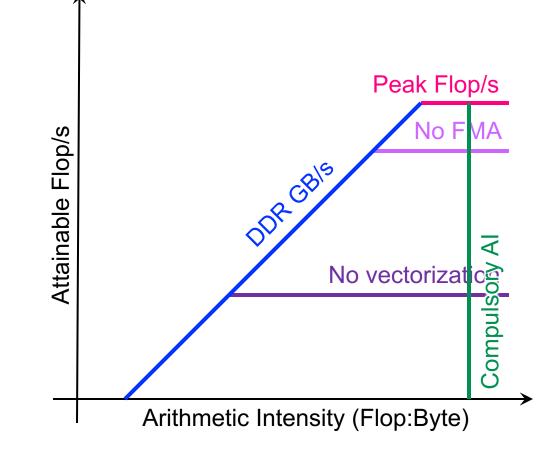

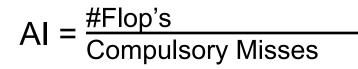

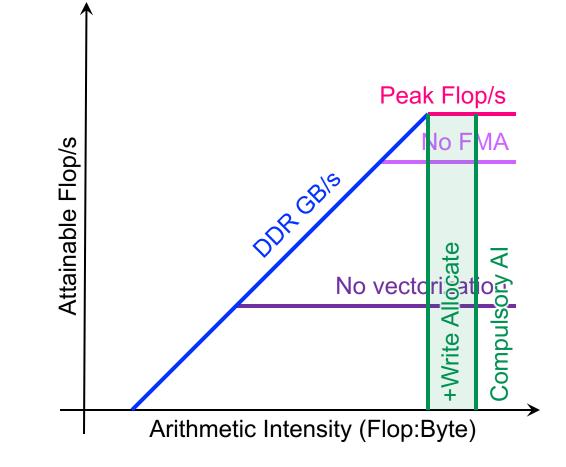

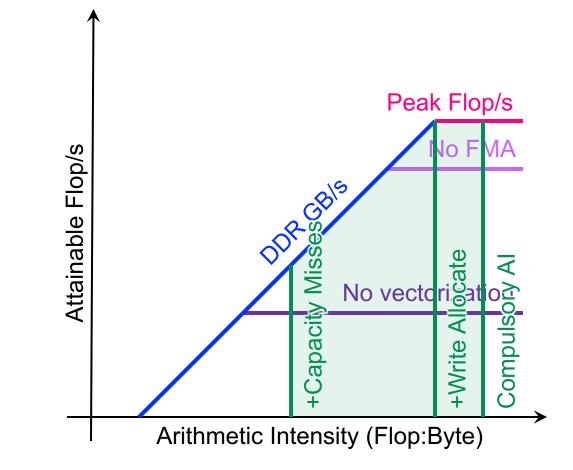

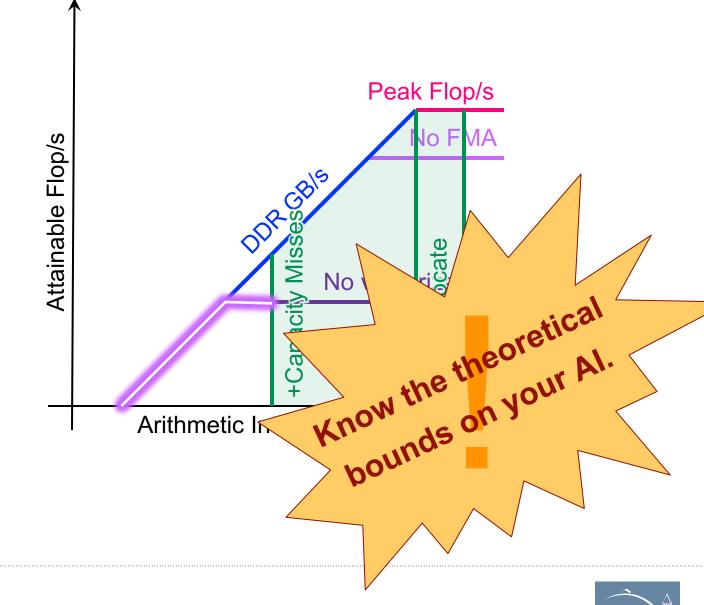

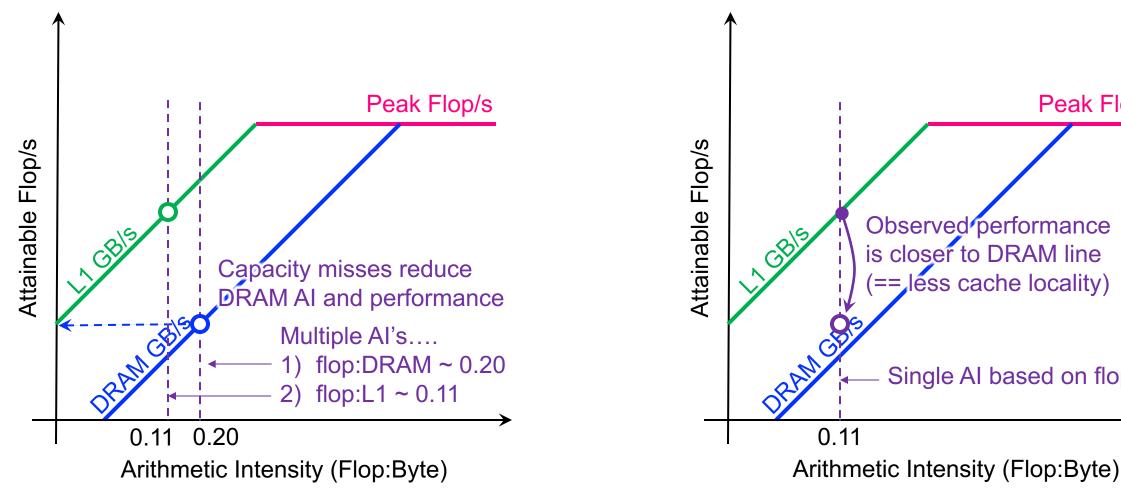

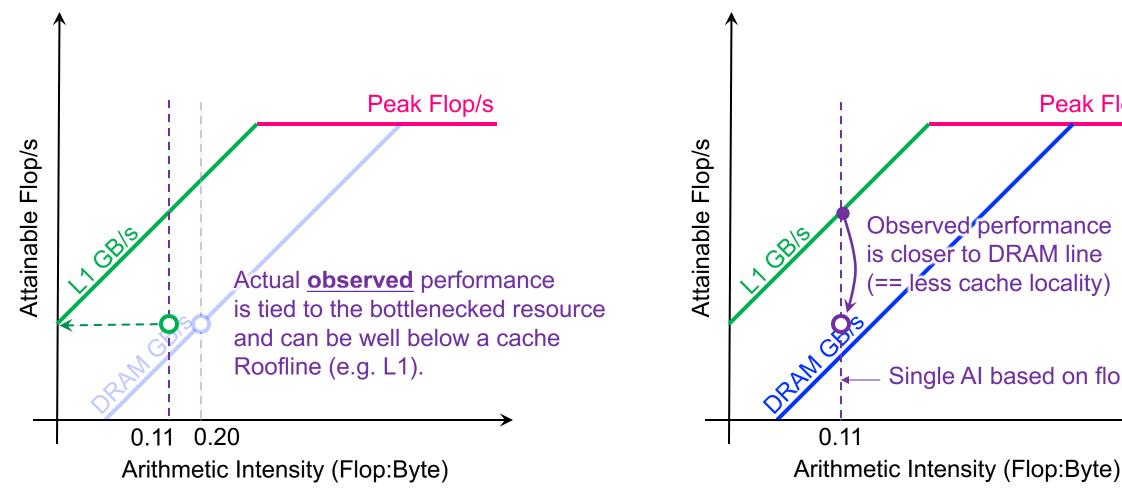

Naively, we can bound AI using only compulsory cache misses

- Naively, we can bound AI using only compulsory cache misses

- However, write allocate caches can lower Al

$AI = \frac{\#Flop's}{Compulsory Misses + Write Allocates}$

- Naively, we can bound AI using only compulsory cache misses

- However, write allocate caches can lower Al

- Cache capacity misses can have a huge penalty

### $AI = \frac{\#Flop's}{Compulsory Misses + Write Allocates + Capacity Misses}$

- Naively, we can bound AI using only compulsory cache misses

- However, write allocate caches can lower Al

- Cache capacity misses can have a huge penalty

- Compute bound became memory bound

### $AI = \frac{\#Flop's}{2}$

Compulsory Misses + Write Allocates + Capacity Misses

ERKELEY NATIONAL LABORATORY

# **Roofline Model:** General Strategy Guide

Broadly speaking, there are three approaches to improving performance:

- Broadly speaking, there are three approaches to improving performance:

- Maximize in-core performance (e.g. get compiler to vectorize)

- Broadly speaking, there are three approaches to improving performance:

- Maximize in-core performance (e.g. get compiler to vectorize)

- Maximize memory bandwidth (e.g. NUMA-aware allocation)

- Broadly speaking, there are three approaches to improving performance:

- Maximize in-core performance (e.g. get compiler to vectorize)

- Maximize memory bandwidth (e.g. NUMA-aware allocation)

- Minimize data movement (increase AI)

LAWRENCE BERKELEY NATIONAL LABORATORY

# Performance Tools

### Machine Characterization

- Application Instrumentation (timing breakdowns)

- Performance Analysis

# **Overview**

- Timers

- Performance Counters

- Simulators / Code introspection (slow)

- Sampling (data is meaningless if it falls below sampling granularity)

- Timeline

- Time-integrated (seconds)

Throughput-oriented (Gflop/s or GB/s)

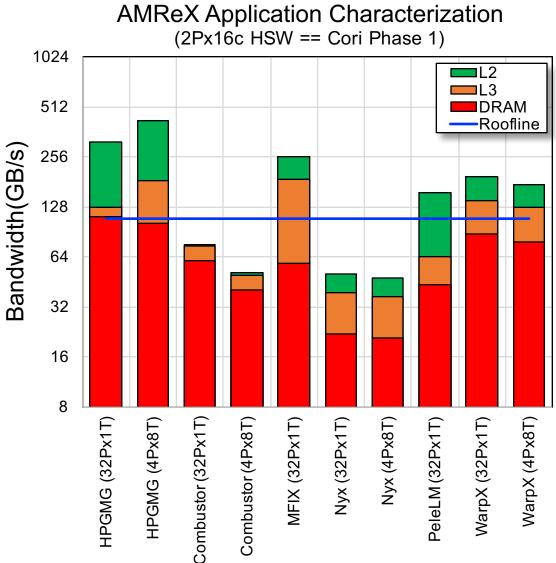

# **Node Characterization**

- "Marketing Numbers" can be deceptive...

- Pin BW vs. real bandwidth

- TurboMode / Underclock for AVX

- compiler failings on high-AI loops.

- LBL developed the Empirical Roofline Toolkit (ERT)...

- Characterize CPU/GPU systems

- Peak Flop rates

- Bandwidths for each level of memory lacksquare

- **MPI+OpenMP/CUDA == multiple GPUs** •

# **Manual Instrumentation**

- Application developers know best...

- $\circ$  What to time

- What to record (e.g. solver iterations, dimensions, etc...)

- $\circ$   $\,$  How asynchrony is exploited

- How the same function might be called/used many different ways == unique timers

- o Computational load imbalance (i.e. understand why timing shows imbalance)

- Make timing instrumentation a first-class citizen when developing an application

- Create timing wrapper that uses either...

- o omp\_get\_wtime()

- o MPI\_Wtime()

- o rdtsc or equivalent

### ue timers ice) I **developing**

## LIKWID

- LIKWID provides easy to use wrappers for measuring performance counters...

- Works on NERSC production systems  $\checkmark$

- Minimal overhead (<1%)  $\checkmark$

- Scalable in distributed memory (MPI-friendly)  $\checkmark$

- Fast, high-level characterization  $\checkmark$

- No detailed timing breakdown or optimization advice Χ

- Limited by quality of hardware performance counter X implementation (garbage in/garbage out)

### Useful tool that complements other tools

https://github.com/RRZE-HPC/likwid

http://www.nersc.gov/users/software/performance-and-debugging-tools/likwid

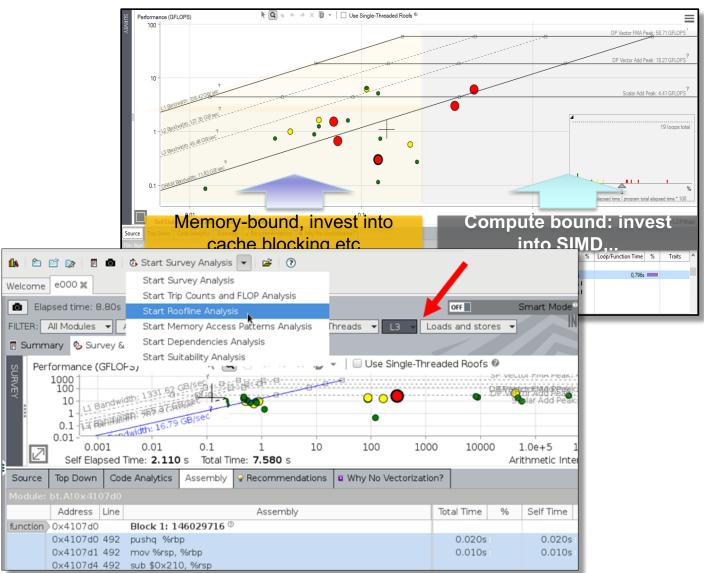

# Intel Advisor

### Includes Roofline Automation...

- Automatically instruments applications (one dot per loop nest/function)

- Computes FLOPS and AI for each function (CARM)

- ✓ AVX-512 support that incorporates masks

- Integrated Cache Simulator<sup>1</sup>

(hierarchical roofline / multiple Al's)

- Automatically benchmarks target system (calculates ceilings)

- Full integration with existing Advisor capabilities

### http://www.nersc.gov/users/training/events/roofline-training-1182017-1192017

<sup>1</sup>Technology Preview, not in official product roadmap so far.

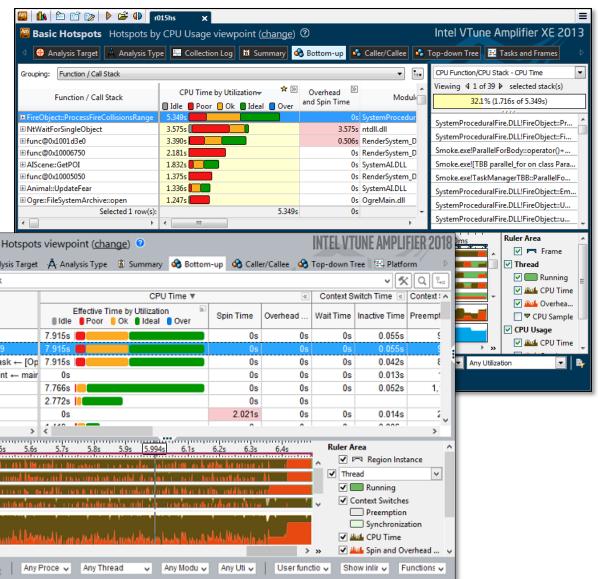

# **Intel VTune**

- Automatically instruments applications (sampling)

- Presents time-oriented execution

- ✓ Has access to performance counters (e.g. %bandwidth, frontend bound, etc...)

- ✓ Hotspot, Concurrency, Synchronization, and Memory **Analysis Options**

Advanced Hotspots Hotspots viewpoint (change)

| Collection Log         | 💮 Analysis Target | 🖧 Analysis Type | 🛔 Summary | 🗞 Bottom-up | 😪 Caller/Calle |

|------------------------|-------------------|-----------------|-----------|-------------|----------------|

| Grouping: Function / C | all Stack         |                 |           |             |                |

|                                                                                                             |                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CPU Time 🔻                                                                  |                                                             |                                                          |            |           |     |  |

|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------|------------|-----------|-----|--|

| Function / Call \$                                                                                          | () Idle                                                                                                                                                     | Effective<br>Poor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                             |                                                             |                                                          | Spin Time  | Overh     |     |  |

| ▼ updateBusinessAccount                                                                                     |                                                                                                                                                             | 7.915s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                             |                                                             |                                                          |            | 0s        |     |  |

| main\$omp\$parallel_f                                                                                       | or@269                                                                                                                                                      | 7.915s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                             |                                                             |                                                          |            | 0s        | T   |  |

| kmp_invoke_r                                                                                                | nicrotask ← [Op                                                                                                                                             | 7.915s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                             |                                                             |                                                          |            | 0s        |     |  |

| ▶ s updateBusinessAccount ← mair                                                                            |                                                                                                                                                             | 0s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                             |                                                             |                                                          |            | 0s        |     |  |

| ▶ updateCustomerAccour                                                                                      | 7.766s                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                             |                                                             |                                                          | 0s         |           |     |  |

| _kmpc_atomic_fixed8                                                                                         | 2.772s                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                             |                                                             |                                                          | 0s         |           |     |  |

| kmpc_critical                                                                                               |                                                                                                                                                             | 0s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                             |                                                             |                                                          |            | 2.021s    |     |  |

| <                                                                                                           | >                                                                                                                                                           | <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                             |                                                             |                                                          |            | ^         |     |  |

| Q*Q+Q-Q+<br>OMP Worker Thread<br>OMP Worker Thread<br>rtmtest_openmp (TID:<br>OMP Worker Thread<br>CPU Time | 5.55 5.65<br>In the activity of the<br>maximum of the<br>official control of the<br>International Control<br>International Control<br>International Control | 5,75<br>2004 - 10<br>102-004 0<br>2020 0<br>2000 0<br>2020 0<br>2000 0<br>20000 0<br>2000 0<br>2000 0<br>2000 0<br>2000 0<br>2000 0<br>0<br>0000 0<br>0000 0<br>0000 0<br>0000 0<br>0000 0<br>0000 0<br>0000 0<br>0000 0<br>0000 0<br>0000 0<br>000000 | 5.8s<br>II. addarodd<br>a ar concalco<br>a ar colocallan<br>a ar colocallan | 5.9s<br>E ta a bi<br>It ta a bi<br>It ta a bi<br>It ta a bi | 5.994s<br>da o b<br>da o b<br>da o b<br>da o b<br>da o b | 6.1s       | 6.2s 6.3s | 6,4 |  |