# Roofline on GPUs (advanced topics)

## Samuel Williams

Computational Research Division Lawrence Berkeley National Lab SWWilliams@lbl.gov

# Acknowledgements

Materials were provided by Nan Ding, Charlene Yang, Yunsong Wang, Khaled Ibrahim, and Thorsten Kurth

- This material is based upon work supported by the Advanced Scientific Computing Research Program in the U.S. Department of Energy, Office of Science, under Award Number DE-AC02-05CH11231.

- This material is based upon work supported by the DOE RAPIDS SciDAC Institute.

- This research used resources of the National Energy Research Scientific Computing Center (NERSC) which is supported by the Office of Science of the U.S. Department of Energy under contract DE-AC02 05CH11231

- This research used resources of the Oak Ridge Leadership Facility at the Oak Ridge National Laboratory, which is supported by the Office of Science of the U.S. Department of Energy under Contract No. DE-AC05-000R22725.

# Roofline for Deep Learning i.e. "Roofline for TensorFlow"

Charlene Yang, Thorsten Kurth, Samuel Williams, "Hierarchical Roofline Analysis for GPUs: Accelerating Performance Optimization for the NERSC-9 Perlmutter System", Cray User Group (CUG), May 2019.

### Performance of DL is as important as simulation

- DOE is beginning to incorporate DL into simulation and analysis

- Training can be extremely computationally expensive

- Performance analysis/optimization of DL can be as important as performance analysis of simulation.

- Can Roofline be used to...

- Quantify efficiency of Deep Learning frameworks? Ο

- Motivate optimizations to improve framework performance? Ο

- Identify facets of architectures should be emphasized to accelerate DL for science? Ο

## conv2d from TensorFlow

- Demonstrate Roofline methodology using TensorFlow+cuDNN

- Setup...

input image = tf.random uniform(shape=input size, minval=0., maxval=1., dtype=dtype) output\_result = conv2d(input\_image, 'NHWC', kernel\_size, stride\_size, dtype)

Forward Pass (2D conv)

exec op = output result

Backward Pass (2D conv + derivative)

opt = tf.train.GradientDescentOptimizer(0.5)

exec op = opt.compute gradients(output result)

Charlene Yang, Thorsten Kurth, Samuel Williams, "Hierarchical Roofline Analysis for GPUs: Accelerating Performance Optimization for the NERSC-9 Perlmutter System", Cray User Group (CUG), May 2019.

## conv2d from TensorFlow

- Each TensorFlow kernel includes multiple sub-kernels

- Padding, permutations, conversions, compute, etc...

- Should include all of them when analyzing performance

- TensorFlow also includes an autotuning step

- Must ignore autotuning when profiling/modeling...

- nvprof --profile-from-start off

- o run 5 warmup iterations (autotuning / not profiled)

- o start profiler (pyc.driver.start\_profiler), run 20 iterations, stop profiler

- Sum up DP, SP, HP metrics. Scale NVProf TC utilization metric

### Vary parameters to understand effects on performance

Charlene Yang, Thorsten Kurth, Samuel Williams, "Hierarchical Roofline Analysis for GPUs: Accelerating Performance Optimization for the NERSC-9 Perlmutter System", Cray User Group (CUG), May 2019.

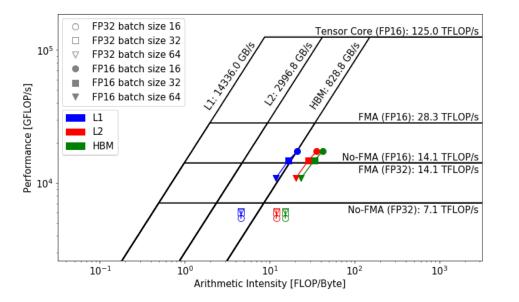

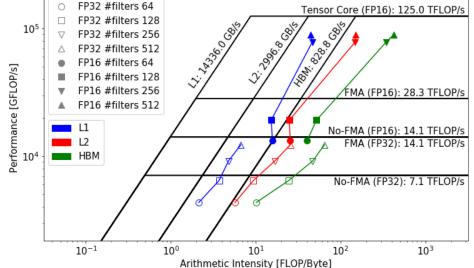

## **TensorFlow / Forward Pass**

### **Batch Size**

- FP16 performance anti-Ο correlated with batch size

- Performance << TC peak Ο

- Transformation kernels

- Low L2 locality Ο

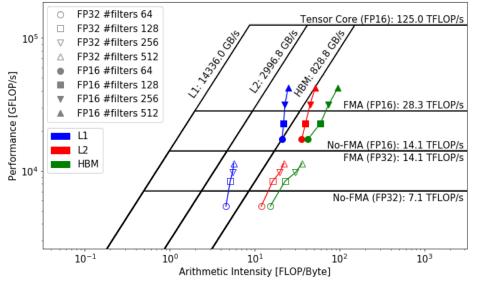

### **#Filters**

- Intensity  $\propto$  #Filters Ο

- Low L2 data locality Ο

- Some use of TC's (>FP16 0 FMA)... partial TC ceiling

- Ο

- Ο

- Ο

- Ο

Charlene Yang, Thorsten Kurth, Samuel Williams, "Hierarchical Roofline Analysis for GPUs: Accelerating Performance Optimization for the NERSC-9 Perlmutter System", Cray User Group (CUG), May 2019.

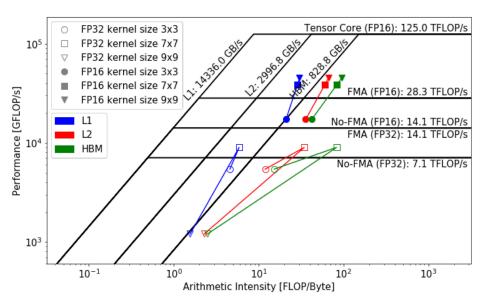

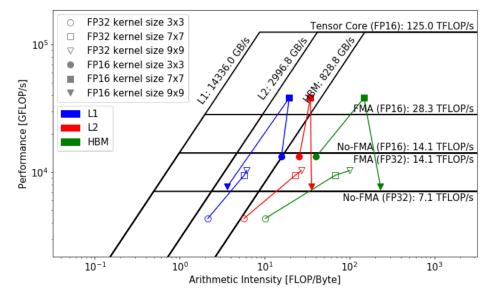

### **Kernel Size** Intensity $\propto$ kernel size Low L2 data locality **Autotuner switched FP32** algorithm to FFT at 9x9 Some use of TC's (>FP16 FMA)... partial TC ceiling

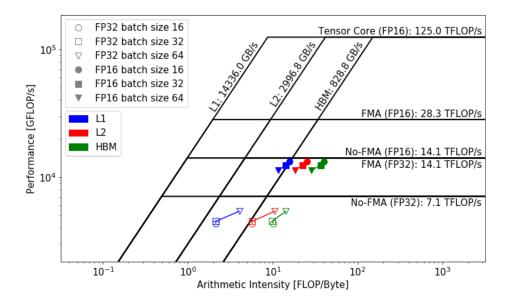

## **TensorFlow / Backward Pass**

### **Batch Size**

Autotuner chose different (**better**) algorithm for FP32 with batch size = 64 (boost)

### **#Filters**

- Close to FP16 TC peak 0

- Close to FP32 FMA peak  $\bigcirc$

- Ο

- $\bigcirc$

### **Kernel Size**

### Good FP32 performance trend (almost peak)

### Autotuner chose to run 9x9 FP16 in FP32 !!

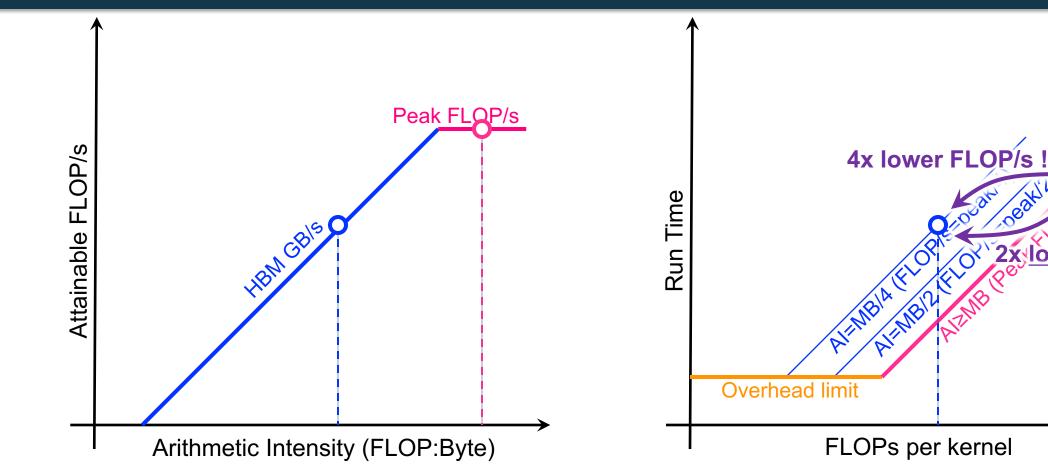

## How do you compare different algorithms?

- Imagine 2 kernels solve the same problem using different algorithms

- We're used to thinking one with higher FLOP/s is better

- Original Roofline is about FLOP/s

- Need alternate time-based version to compare optimizations that change the number of FLOPs

## **Tensor Flow Takeaway**

- Performance rarely anywhere close to FP16 peak

- Serializing compute and data permutation kernels drives down AI Ο

- Changing algorithms or precisions can confuse Roofline Analysis Ο

- Need alternate time formulation of Roofline *i.e. differentiating architectural efficiency from algorithmic efficiency*

- > Need a better way of analyzing mixed precision codes *i.e. understanding bottlenecks when mixing FP32, FP16, and tensor core instructions*

- Migrating from NVProf to Nsight Compute

- More accurate WMMA counts  $\bigcirc$

- >10x faster  $\bigcirc$

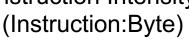

# Instruction Roofine Model "FLOP/s aren't that important to me"

Nan Ding, Samuel Williams, "An Instruction Roofline Model for GPUs", Performance Modeling, Benchmarking, and Simulation (PMBS), November, 2019

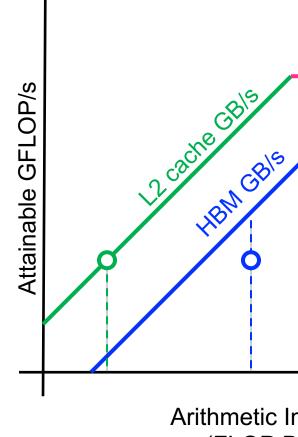

## How do we go beyond the FLOP Roofline?

- Think about classifying applications by instruction mix...

- Heavy floating-point (rare in DOE) Ο

- Mix of integer and floating-point Ο

- Integer-only (e.g. bioinformatics, graphs, etc...) Ο

- Mixed precision Ο

### • FLOP/s $\rightarrow$ IntOP/s $\rightarrow$ FLOP/s+IntOP/s

- Adopted by Intel Advisor

- Useful when wanting to understand 'performance' rather than bottlenecks Ο

- What is an "Integer Op"? LEA but not an SIB byte? Ο

- Instruction Fetch/Decode/Issue bottlenecks?  $\bigcirc$

- **Functional Unit Bottlenecks?**  $\bigcirc$

- Need to create a true instruction Roofline

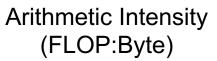

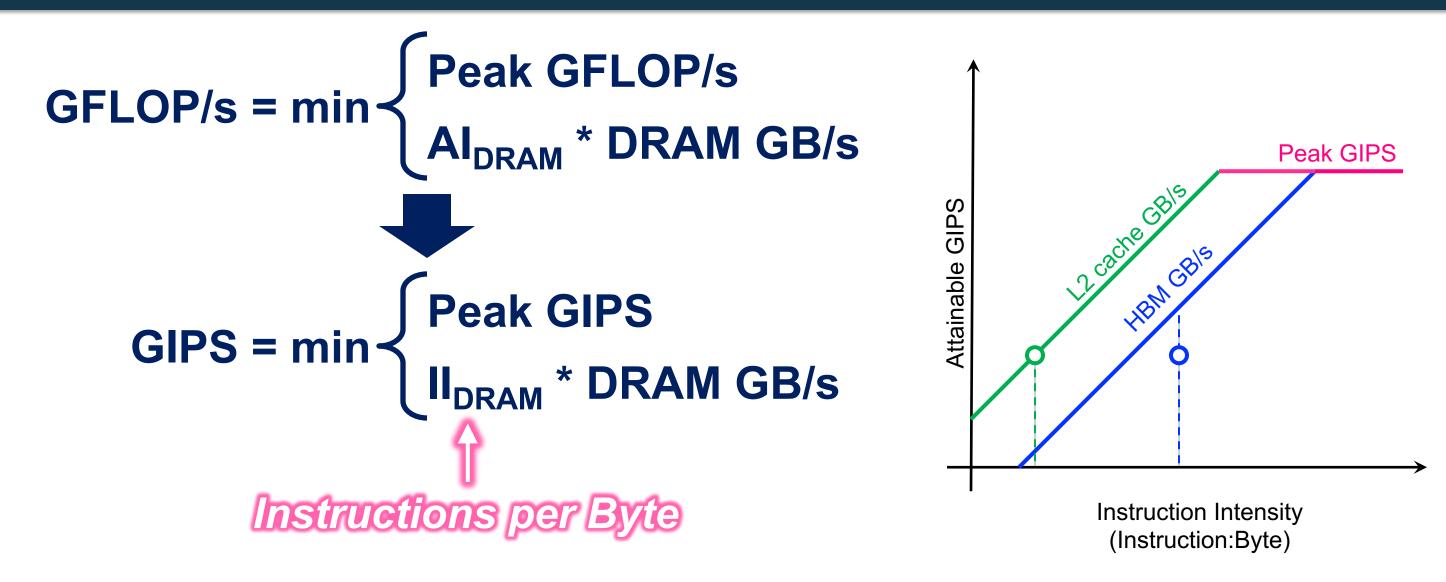

## **NVIDIA GPU Instruction Roofline**

- Instructions/second? Instructions per Byte?

- What is an 'Instruction' on a GPU?

- Thread-level hides issue limits?  $\bigcirc$

- Warp-level hides predication effects? Ο

- Scale non-predicated threads down by the warp size (divide by 32) Ο

- Show warp instructions per second Ο

- Break instructions into subclasses (integer, FP32, FP64, LDST, WMMA) 0

- Naively, one would think instruction intensity should use 'bytes' Matches well to existing Roofline; works with well-known bandwidths Ο

- GPUs access memory using 'transactions'

- 32B for global/local/L2/HBM Ο

- 128B for shared memory Ο

- "Instructions/Transaction" preserves traditional Roofline, but enables a new way of understanding memory access

### **Instruction Roofline**

### Instruction Roofline

### Instruction Roofline on GPUs

As the natural quanta for GPU memory access is a "transaction"....

Instruction Intensity

### Instruction Roofline on GPUs

Instruction Intensity (Instruction:Transaction)

Instructions / Transactions (to/from level "x")

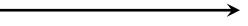

## Instruction Roofline on NVIDIA GPUs

### Instruction Intensity (II)

- (Warp or equivalent) Instructions / Transaction Ο

- Refine into L1 (global+local+shared), L2, HBM Instruction Intensities Ο

- Further refine based on instruction type (LDST instructions / global transaction) Ο

### **Peak Performance and Peak Bandwidths**

### Instruction: Ο

- 80 SMs \* 4 warps \* 1.53GHz ~ 490 GIPS (warp-level) 0

- Use ERT for memory (convert from GB/s) Ο

- L1: 80 SMs \* 4 transactions/cycle \* 1.53 GHz ~ 490 GTXN/s Ο

- L2: 94 GTXN/s (empirical) 0

- HBM: 26 GTXN/s (empirical) 0

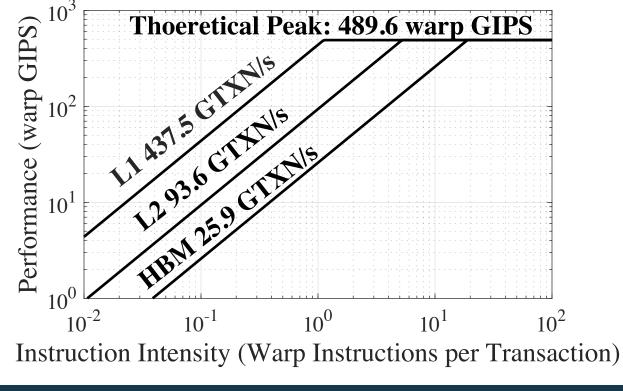

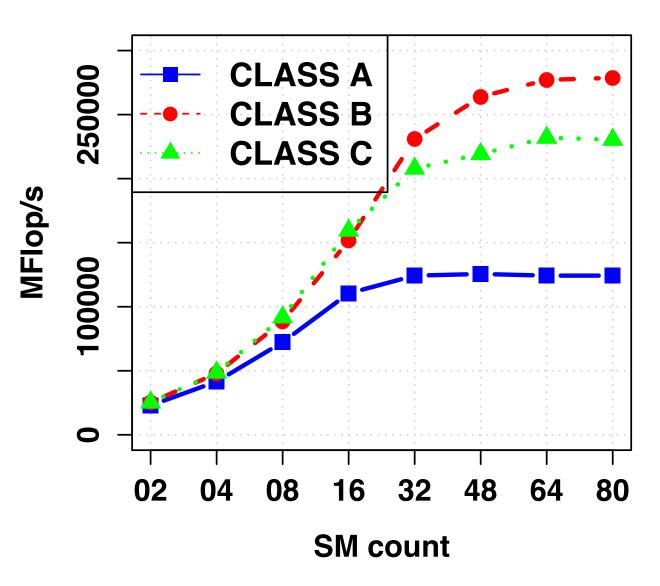

## Efficiency of Global Memory Access

- (Global)LDST Instruction Intensity has a special meaning / use...

- **Global LDST instructions / Global transactions**  $\bigcirc$

- Numerator lower than nominal II  $\bigcirc$

- Denominator can be lower than nominal L1 II (no local or shared transactions) Ο

- Denotes efficiency of memory access

- 3 "Walls" of interest:

- ≥1 transaction per LDST instruction Ο (all threads access same location)

- ≤32 transactions per LDST instruction Ο (gather/scatter or stride>=128B)

- Unit Stride: 1 LDST per 8 transactions Ο (double precision)

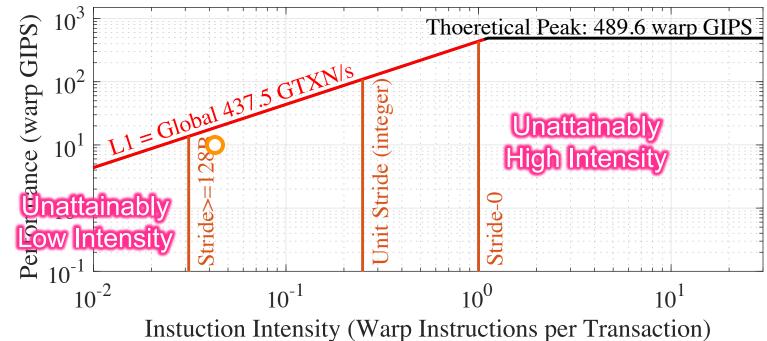

## Efficiency of Shared Memory Access

- (Shared)LDST Instruction Intensity also has a special meaning / use

- Shared LDST instructions / Shared transactions  $\bigcirc$

- It is similarly loosely related to nominal II Ο

- Can be used to infer the number of bank conflicts

- 2 "Walls" of interest:

- Minimum of 1 transaction per shared Ο LDST instruction (*no bank conflicts*)

- Maximum of 32 transactions per Ο shared LDST instruction (all threads access different lines in the same bank)

BERKELEY

### **Instruction Roofline for Smith-Waterman**

- Integer-only Alignment code on NVIDIA GPU

- No predication effects, but inefficient global memory access

Nan Ding, Samuel Williams, "An Instruction Roofline Model for GPUs". PMBS. November. 2019.

BERKELEY LAB

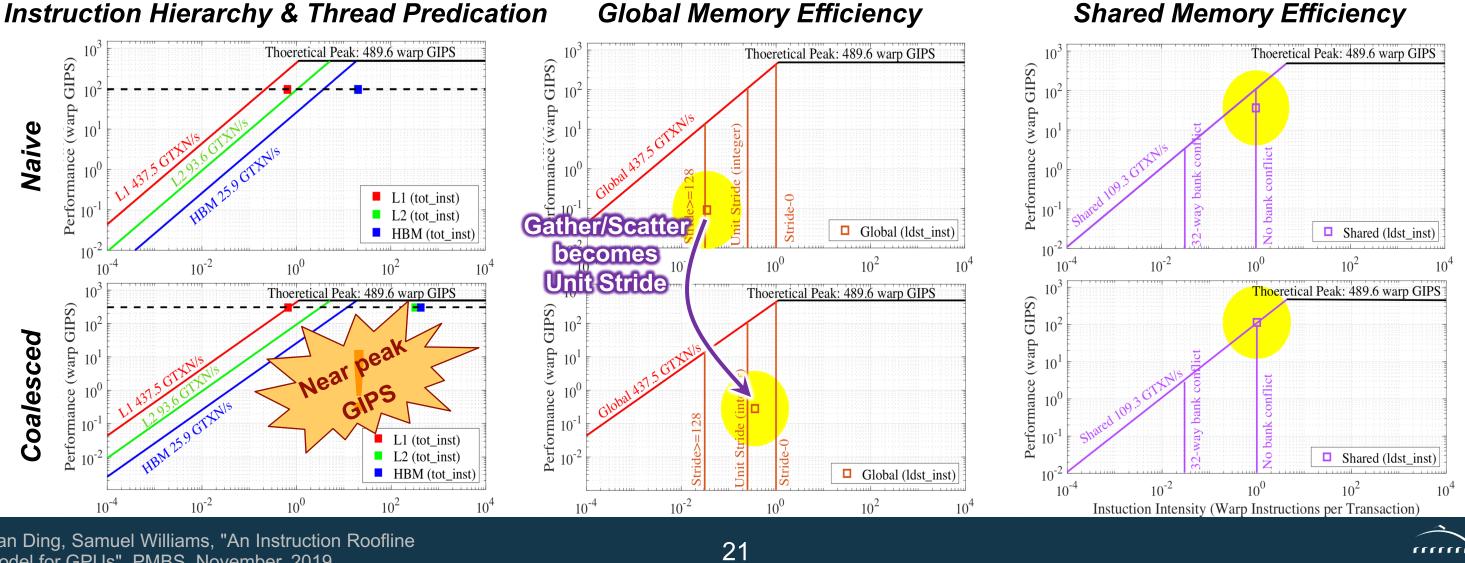

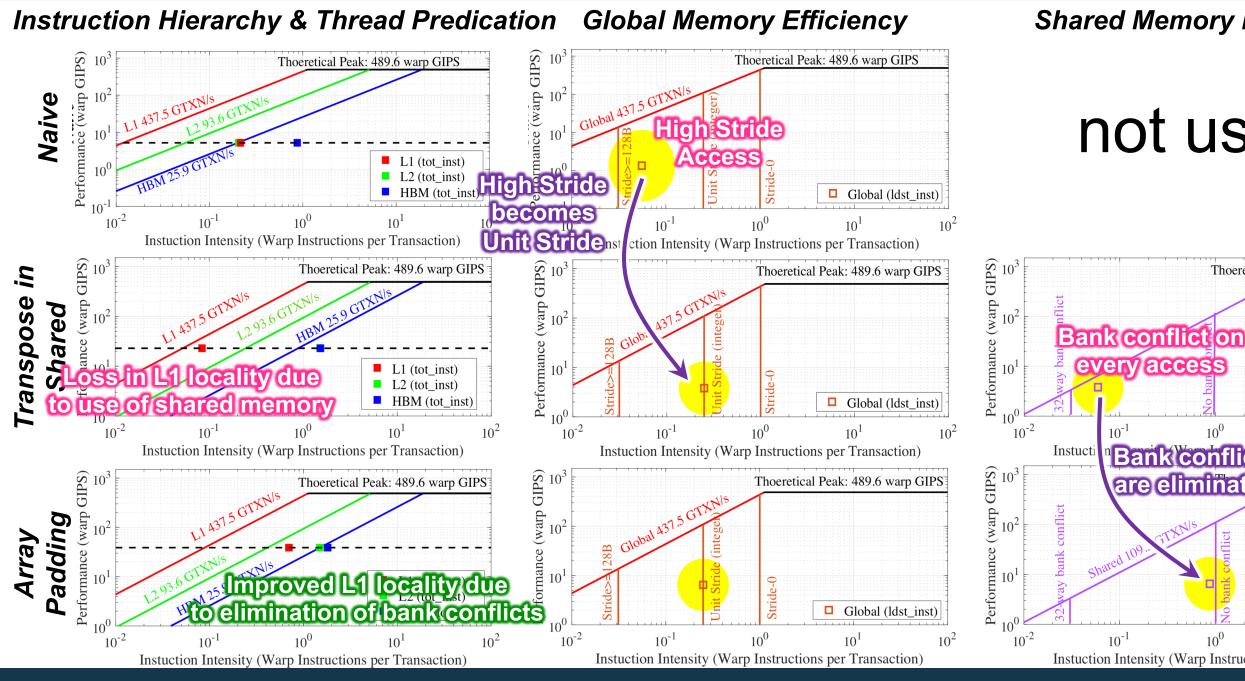

## Instruction Roofline for Matrix Transpose

Nan Ding, Samuel Williams, "An Instruction Roofline Model for GPUs". PMBS. November. 2019.

22

### Shared Memory Efficiency

### not used

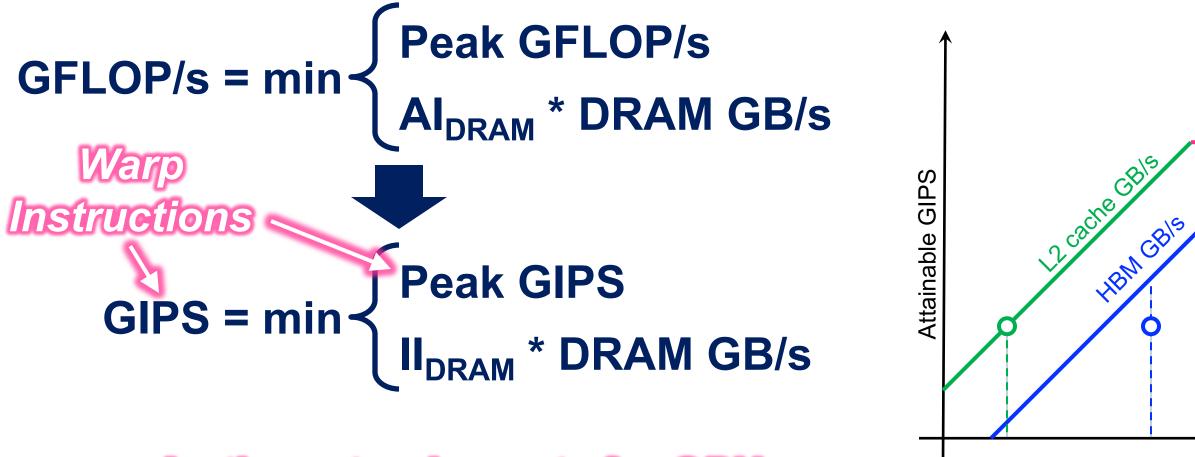

## **Other Uses of Instruction Roofline**

### Predication

- Individual threads can mask out execution when in branch-not-taken Ο

- 16 FLOPs/SM/cycle... 1 FP warp every 2 cycles Ο

1 FP warp every cycle with half threads predicated

- Use performance metrics to plot both warp GIPS and non-predicated threads (scaled by 32) Ο

- FMA, Tensor Cores, Mixed Precision, ...

- Rather than counting FLOPs, count GIPS Ο

- Can differentiate total instruction issue bandwidth from functional unit utilization (FP32, FP64)  $\bigcirc$

- n.b., some GIPS should be summed (FP16+FP32) while others are have dedicated pipelines Ο (FP64, TC)

## Instruction Roofline Takeaway

### **Traditional Roofline**

- Tells us about performance (floating-point)

- Use of FMA, SIMD, vectors, tensors has no affect on intensity, but may <u>increase</u> performance...

- Presence of integer instructions has no affect on intensity, but may decrease performance

- Reducing precision (64b, 32b, 16b) increases arithmetic intensity

### **Instruction Roofline**

- Tells us about bottlenecks *(issue and memory)*

- Use of FMA, SIMD, vectors, tensors decreases intensity and may decrease "performance"

- Presence of integer instructions increases intensity and might increase performance.

- Reducing precision has no affect on intensity

### **Memory Walls**

- (memory access)

- LDST instructions)

**Tells us about efficiency**

Intensity based on LDST instructions and transactions

Predication could affect intensity (could have zero transactions for a LDST instruction, but not all

Reducing precision shifts intensity, and the unit-stride wall

## Instruction Roofline on Vector CPUs?

### Instruction Roofline on GPUs

- Warp-based  $\rightarrow$  easy to see functional unit contention

- LDST instructions generate multiple transactions  $\rightarrow$  memory walls

Predication effects inferred through differences in (scaled) thread GIPS and warp GIPS

### Instruction Roofline on CPUs micro-op (uOP) based $\rightarrow$ easy to see

- functional unit contention

- Memory walls can only be constructed if VGATHER/VSCATTER generate *multiple cache performance counter* events

- Masking/Predication effects can only be inferred if there are counts for individual vector lanes

# Roofline Scaling Trajectories "Is my code ready for Perlmutter, Frontier, ..."

Khaled Ibrahim, Samuel Williams, Leonid Oliker, "Performance Analysis of GPU Programming Models using the Roofline Scaling Trajectories", Bench, November, 2019.

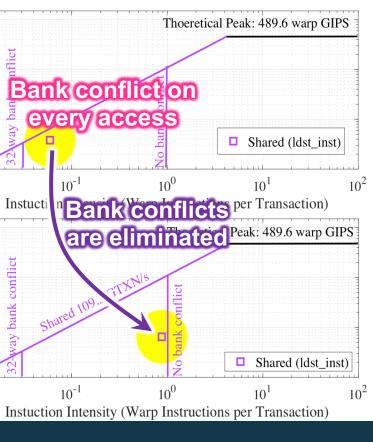

## Understanding SM Scalability is hard

- Control SM count on Volta GPUs

- LU NAS Parallel benchmark (in CUDA)

- Typical Scaling Plot

- Provide performance with SM change,

- No insights into root causes.

- Why Class B scale better than A,

- o but Class C is not better than B?

### Khaled Ibrahim, Samuel Williams, Leonid Oliker, "Performance Analysis of GPU Programming Models using the Roofline Scaling Trajectories", Bench, November, 2019.

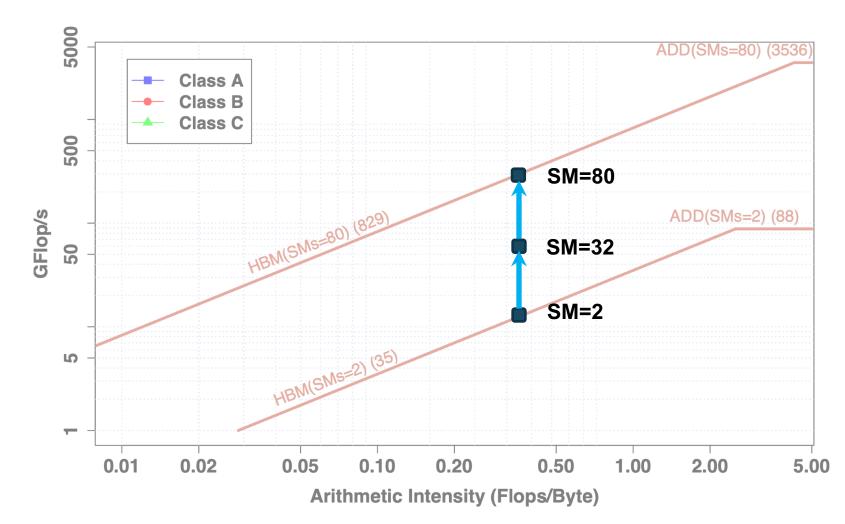

## **Roofline Scaling Trajectory**

- Replot SM scalability as a trendline on the Roofline

- Define compute and bandwidth ceilings as a function of #SMs

### Ideal behavior:

$\Delta y$  = increase in computational resources or share of BW

$\Delta x=0$  (No change in arithmetic intensity)

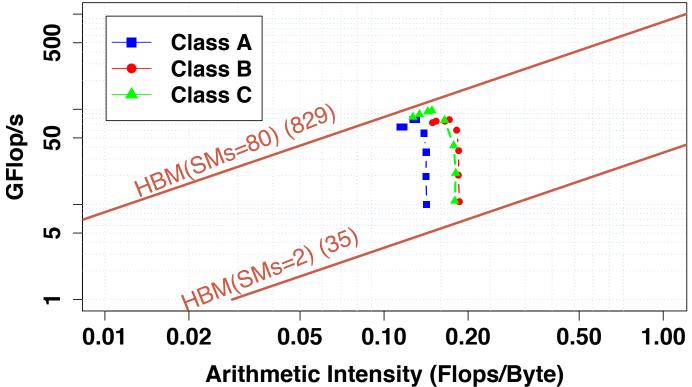

## Example #1 – NAS MG in OpenACC

- Performance scales nearly linearly until high concurrency

- Fall over in performance...

- **HBM** limited  $\bigcirc$

- Exhausts cache capacity Ο

- More SMs generate more capacity Ο misses

- AI degrades Ο

- Performance degrades Ο

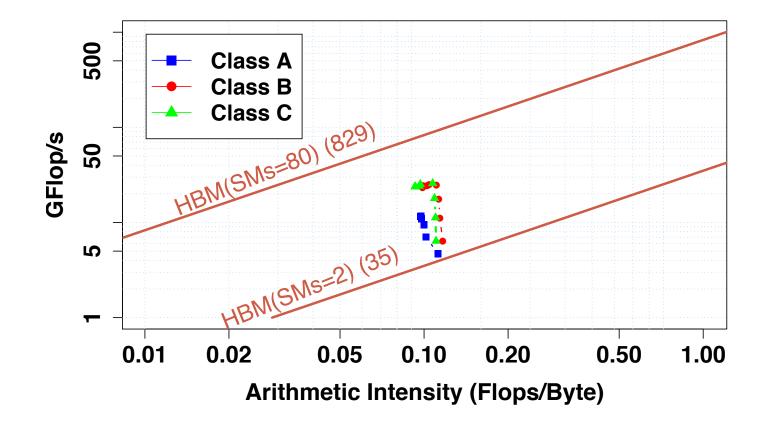

## Example #2 – NAS FT in OpenACC

- Performance scales poorly

- Saturation in performance far below HBM ceiling

- Limited degradation in AI (few capacity misses)

Khaled Ibrahim, Samuel Williams, Leonid Oliker, "Performance Analysis of GPU Programming Models using the Roofline Scaling Trajectories", Bench, November, 2019.

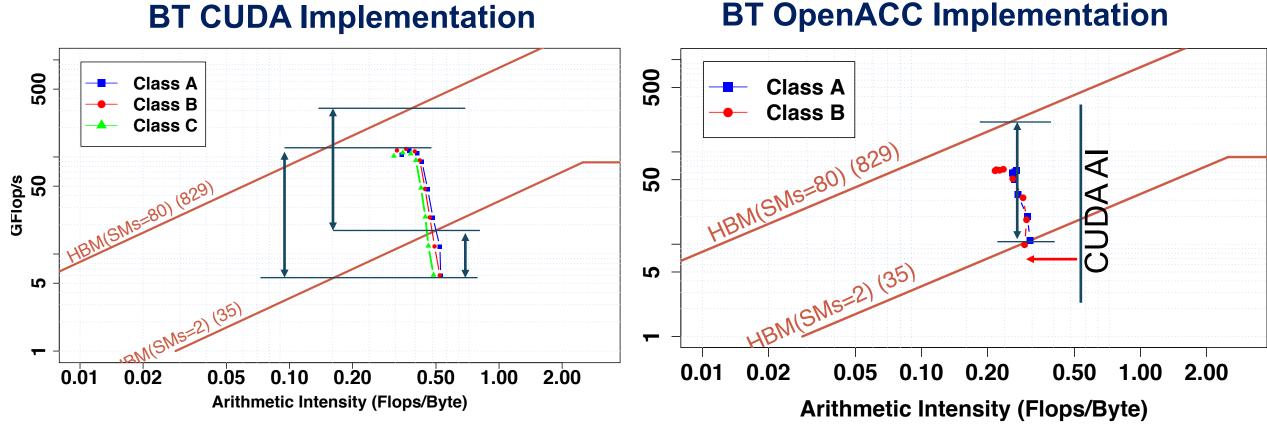

## **Understanding Different Programming Models**

- CUDA delivered better AI and better scalability

- But CUDA efficiency was initially much lower Different compilers/PM have different challenges

Williams. Oliker. Ibrahim Samuel Leonid Khaled "Performance Analysis of GPU Programming Models using the Roofline Scaling Trajectories", Bench, November, 2019.

## Summary

- Recasts thread scalability into the Roofline model

- Quantitative analysis of different implementations, programming models, or compilers

- Infer cache behavior and efficiency

Codes that demonstrate a good Roofline Scaling Trajectory will likely scale to Perlmutter, Frontier, and Aurora

Khaled Ibrahim Samue Williams. Leonid Oliker. "Performance Analysis of GPU Programming Models using the Roofline Scaling Trajectories", Bench, November, 2019.